<input id="kc8ii"></input>

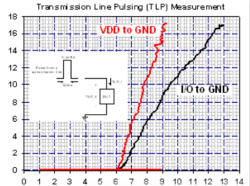

對某些人來說ESD是一種挑戰,因為需要在處理和組裝未受保護的電子元件時不能造成任何損壞。這是一種電路設計挑戰,因為需要保證系統承受住ESD的沖擊,之后仍能正常工作,更好的情況是經過ESD事件后不發生用戶可覺察的故障。

與人們的常識相反,設計人員完全可以讓系統在經過ESD事件后不發生故障并仍能繼續運行。將這個目標謹記在心,下面讓我們更好地理解ESD沖擊時到底發生了什么,然后介紹如何設計正確的系統架構來應對ESD。詳細閱讀>>

干貨

干貨

元器件靜電放電隱患貫穿元器件設計、生產、檢驗、交接、運輸、使用全過程,通用的防護手段不可或缺,但為滿足新型號用元器件的發展對靜電防護技術的提升需求,需要建立系統性、工程性的靜電防護體系,遵循靜電防護與全面質量管理相結合,靜電防護與關鍵工序質量控制相結合,靜電防護堅持領導、技術人員、基層員工三結合的原則,控制元器件靜電放電損傷質量問題的產生,為保障型號元器件可靠性提供了有力的支撐。

?

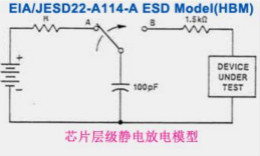

隨著半導體技術的發展,大量集成電路被應用到電子產品中,靜電放電也成為影響電子產品性能的關鍵因素。但是靜電放電針對不同的環境也有不同的差異。最為明顯的就是系統層級靜電放電和芯片層級靜電放電。詳細閱讀>>

?

智能手機設計在經歷電磁兼容測試時候總是會出現或多或少的ESD靜電放電抗擾問題,這些ESD問題都分布在哪里呢?主要是些什么樣的ESD靜電放電問題?有什么大的問題和后果?詳細閱讀>>

?

為實現十倍于USB2.0的傳輸速度,USB 3.0控制芯片必須使用更先進的制程來設計與制造,這也造成控制芯片對ESD的耐受能力快速下降。USB 3.0會被大量用來傳輸影音數據,對數據傳輸容錯率會有越嚴格的要求,必要使用額外的保護組件來防止ESD事件對數據傳輸的干擾。詳細閱讀>>

?

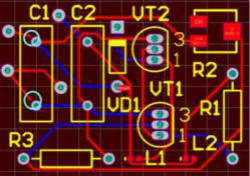

在PCB板的設計當中,可以通過分層、恰當的布局布線和安裝實現PCB的抗ESD設計。通過調整PCB布局布線,能夠很好地防范ESD.盡可能使用多層PCB,相對于雙面PCB而言,地平面和電源平面,以及排列緊密的信號線-地線間距能夠減小共模阻抗和感性耦合,使之達到雙面PCB的1/10到1/100.對于頂層和底層表面都有元器件、具有很短連接線。詳細閱讀>>

?

靜電,通常都是人為產生的,如生產、組裝、測試、存放、搬運等過程中都有可能使得靜電累積在人體、儀器或設備中,甚至元器件本身也會累積靜電,當人們在不知情的情況下使這些帶電的物體接觸就會形成放電路徑,瞬間使得電子元件或系統遭到靜電放電的損壞(這就是為什么以前修電腦都必須要配戴靜電環托在工作桌上,防止人體的靜電損傷芯片),如同云層中儲存的電荷瞬間擊穿云層產生劇烈的閃電,會把大地劈開一樣,而且通常都是在雨天來臨之際,因為空氣濕度大易形成導電通到。詳細閱讀>>

基礎知識

基礎知識

?

為了提高產品的耐受性,影響整個電子業的四個長期趨勢,促使靜電放電(ESD)保護在目的性工程的總體實踐中日益重要。首先,與數年前相比,隨著用戶、信號I/O功能日益復雜和流行,產品上ESD的閃擊進入點多了許多。尤其是對于信號I/O端口,以及小鍵盤、指示器、顯示器。詳細閱讀>>

?

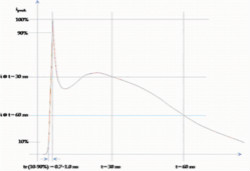

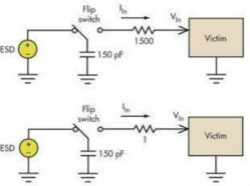

實際上,所有ESD測試標準都涉及了沖擊源模型,例如人體、機器或充電器件。這些模型精確地解釋了測試源的導電特性。最新的測試標準如普遍應用的IEC-61000-4-2,詳述了沖擊波形,進一步將測試源簡化成測試源變量參數,為研究和評估各種高速瞬態緩解辦法提供了關鍵信息。詳細閱讀>>

?

隨著微電子技術的飛速發展,特別是隨著集成電路特征尺寸的減小以及MOS集成電路的廣泛使用,新型集成電路普遍具有線間距短、線細、集成度高、運算速度快、低功率和輸入阻抗高等特點,因而導致這類器件對靜電放電越來越敏感。詳細閱讀>>

ESD的設計學問太深了,這里只是拋磚引玉給大家科普一下了,基本上ESD的方案有如下幾種:電阻分壓、二極管、MOS、寄生BJT、SCR(PNPN structure)等幾種方法。而且ESD不僅和Design相關,更和FAB的process相關,而且學問太深了,這里我也不是很了解,無法給再大家深入了。當然術業專攻學無止境,工作中只有不斷學習才會創收更高效益。

關于我們 | About Us | 聯系我們 | Contact Us | 隱私政策 | 版權申明 | 投稿信箱 | 網站地圖

Copyright ? www.77uud.com? All Rights Reserved

電子元件技術網 版權所有 ??粵ICP備10202284號??粵ICP證B2-20090022

未經版權所有人明確的書面許可,不得以任何方式或媒體翻印或轉載本網站的部分或全部內容。