【導讀】本文提出了一種基于DSP和CMOS圖像傳感器,同時由復雜可編程邏輯控制芯片CPLD控制的實時圖像采集系統的實現方案,不僅在噪聲上得到了有效改善,而且分辨率也得到了明顯提高。

硬件設計

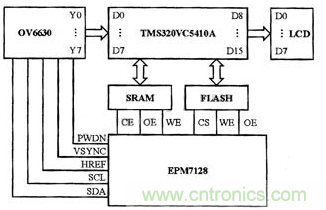

圖1所示是該圖像采集系統的電路結構框圖。由圖1可見,該圖像采集系統主要由OV6630圖像傳感芯片、CPLD控制模塊、SRAM數據存儲器、FLASH程序存儲器、DSP信號處理器等幾部分組成。其圖像采集芯片用美國Omni Vision公司開發的彩色CMOS圖像傳感器OV6630,該芯片與傳統的CCD傳感器相比,其最明顯的優勢是集成度高,功耗小,生產成本低,容易與其它芯片整合。該芯片將CMOS光感應核與外圍支持電路集成在一起。由于其運用了專有的傳感器技術,因而能夠消除普通的光電干擾。該芯片的像素陣列為352×288,即101376像素,還有4行、4列可供選擇。圖像數據的輸出有多種格式(YCrCb4:2:2,GRB4:2:2和RGB原始數據輸出格式),本系統選用8通道Y輸出RGB原始數據輸出格式,以及逐行掃描的工作方式。其輸出格式為:

奇數掃描行BGBG……

偶數掃描行GRGR……

圖1:圖像采集系統結構框圖

根據人眼對彩色響應帶寬不高的大面積著色特點,每個象素沒有必要同時輸出3種顏色。因此,數據采樣時,奇數掃描行的第1,2,3,4,…象素分別采樣和輸出B,G,B,G,…數據;偶數掃描行的第1,2,3,4,…象素分別采樣和輸出G,R,G,R,…數據。在實際處理時,每個象素的R,G,B信號由象素本身輸出的某一種顏色信號和相鄰象素輸出的其他顏色信號構成。這種采樣方式在基本不降低圖像質量的同時,可以將采樣頻率降低60%以上。

系統中的核心處理芯片選用TI公司的加強型定點DSP芯片TMS320VC5410A,該DSP的工作頻率可達160 MHz,內部有64KBRAM空間可以靈活的映射為數據或程序存儲空間。由于DSP的內部存儲空間有限,所以,本設計在外部擴展了一大小為1 MB的SRAM數據存儲器CY7C1021和256 K的FLASH程序存儲器SST39VF400A。控制芯片CPLD選用Altera公司的MAX7000系列芯片EPM7128SLC84-15。該芯片包含84個I/O管腳、128個宏單元,每16個宏單元可組成一個邏輯陣列塊,工作電壓為5.0 V。該芯片在系統中處于總體時序控制地位,既用于給圖像傳感器芯片提供控制信號。也用于SRAM和FLASH的片選和讀寫控制,同時還負責LCD的顯示控制。

軟件設計

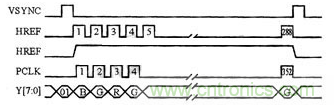

當系統配置完畢以后,便可以進行圖像數據的采集與處理。在采集圖像的過程中,最主要的工作是判別一幀圖像數據的開始和結束的時刻。在仔細研究了OV6630輸出的同步信號(VSYNC是垂直同步信號、HREF是水平同步信號、PCLK是輸出數據同步信號)的基礎上。筆者用VHDL語言實現了采集過程起始點的精確控制。圖2所示為圖像采集期間三個同步信號與數據信號的時序關系圖。

圖2中,每一個幀同步信號VSYNC周期包含288個水平同步信號HREF脈沖,而每一個HREF周期包含352個PCLK時鐘脈沖,每一個PCLK時鐘可輸出一個RGB像素的視頻數據。

圖2:圖像采集時序圖

通過監測系統中的垂直同步信號VSYNC的變化,即可得知新的一幀圖像是否開始,一幀圖像開始后,僅當HREF為高且PCLK輸出下降沿時,才能輸出一個有效的像素值。VSYNC的上升沿表示一幀新的圖像的到來,下降沿則表示一幀圖像數據采集開始(CMOS圖像傳感器是按列采集圖像的)。HREF是水平同步信號,其上升沿表示一列圖像數據的開始。PCLK是輸出數據同步信號。只有當HREF為高電平時,才能開始有效的采集數據,PCLK下降沿的到來表明數據的產生,PCLK每出現一個下降沿可傳輸一位數據。HREF為高電平期間,共可傳輸352位數據。在一幀圖像中,即VSYNC為低電平期間,HREF將出現288次高電平。而當下一個VSYNC信號的上升沿到來時,即表明分辨率為352×288的圖像采集過程的結束。

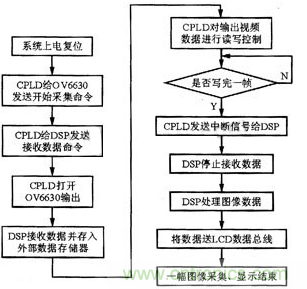

CPLD控制的實現過程首先是按順序檢測VSYNC和CHSYNC信號是否有效,要注意防止毛刺信號的干擾。毛刺信號時間很短,設計時可采用設標志位的方法,即當檢測到信號的有效沿后(對于VSYNC是上升沿,而對于CHSYNC是下降沿),可在等待一定時間后再次檢測信號,看其是否仍然有效,如果有效,則說明信號是正確的。

系統中的像素數據是按PCLK時鐘輸出的,所以,可用來存儲圖像的SRAM使能信號CE。另外,其讀寫信號也是由CPLD產生的。讀信號RE只要在CPLD寫操作中置“1”即可。由于在數據輸出時,PCLK的上升沿信號比較穩定,而RAM可在WR上升沿將數據寫入,因此,可以在HREF有效后(HREF=1)采用PCLK作為寫信號RW。

由于圖像像素點的個數已知,即數據個數已知,故在計數完畢后,CPLD將發出計數完畢信號。而DSP在接收到中止信號后,即可開始讀取RAM中的數據,并對數據進行壓縮和相應的處理,然后把數據放到LCD液晶屏的數據總線,最后將采集到的圖像在液晶屏上顯示出來。圖3為圖像采集系統的軟件流程圖。

圖3:圖像采集系統軟件流程圖

結束語

本系統采用DSP和CPLD的綜合方案來將圖像的采集和數據的處理分而治之。實驗結果表明,該系統圖像清晰,且能滿足實時顯示的要求,可廣泛應用在網絡視頻和工業自動監測等方面。