【導讀】LVDS:Low Voltage Differential Signaling,低電壓差分信號。 LVDS傳輸支持速率一般在155Mbps(大約為77MHZ)以上。

1 、LVDS信號介紹

LVDS:Low Voltage Differential Signaling,低電壓差分信號。

LVDS傳輸支持速率一般在155Mbps(大約為77MHZ)以上。

LVDS是一種低擺幅的差分信號技術,它使得信號能在差分PCB線對或平衡電纜上以幾百Mbps的速率傳輸,其低壓幅和低電流驅動輸出實現(xiàn)了低噪聲和低功耗。

IEEE在兩個標準中對LVDS信號進行了定義。ANSI/TIA/EIA-644中,推薦最大速率為655Mbps,理論極限速率為1.923Mbps。

1.1 LVDS信號傳輸組成

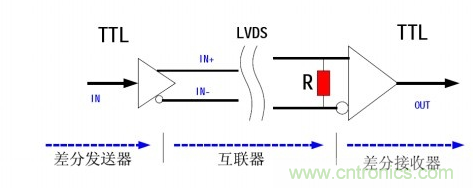

圖1 LVDS信號傳輸組成圖

LVDS信號傳輸一般由三部分組成:差分信號發(fā)送器,差分信號互聯(lián)器,差分信號接收器。

差分信號發(fā)送器:將非平衡傳輸?shù)腡TL信號轉換成平衡傳輸?shù)腖VDS信號。通常由一個IC來完成,如:DS90C031

差分信號接收器:將平衡傳輸?shù)腖VDS信號轉換成非平衡傳輸?shù)腡TL信號。通常由一個IC來完成,如:DS90C032

差分信號互聯(lián)器:包括聯(lián)接線(電纜或者PCB走線),終端匹配電阻。按照IEEE規(guī)定,電阻為100歐。我們通常選擇為100,120歐。

1.2 LVDS信號電平特性

LVDS物理接口使用1.2V偏置電壓作為基準,提供大約400mV擺幅。

LVDS驅動器由一個驅動差分線對的電流源組成(通常電流為3.5mA),LVDS接收器具有很高的輸入阻抗,因此驅動器輸出的電流大部分都流過100Ω 的匹配電阻,并在接收器的輸入端產(chǎn)生大約350mV 的電壓。

電流源為恒流特性,終端電阻在100――120歐姆之間,則電壓擺動幅度為:3.5mA * 100 = 350mV ;3.5mA * 120 = 420mV 。

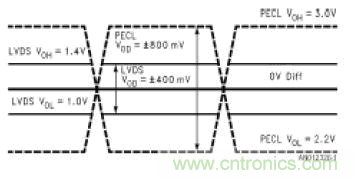

下圖為LVDS與PECL(光收發(fā)器使用的電平)電平變化。

圖2 LVDS與PECL電平圖示

由邏輯“0”電平變化到邏輯“1”電平是需要時間的。

由于LVDS信號物理電平變化在0。85――1。55V之間,其由邏輯“0”電平到邏輯“1”電平變化的時間比TTL電平要快得多,所以LVDS更適合用來傳輸高速變化信號。其低壓特點,功耗也低。

采用低壓技術適應高速變化信號,在微電子設計中的例子很多,如:FPGA芯片的內(nèi)核供電電壓為2。5V或1.8V;PC機的CPU內(nèi)核電壓,PIII800EB為1.8V;數(shù)據(jù)傳輸領域中很多功能芯片都采用低電壓技術。

1.3 差分信號抗噪特性

從差分信號傳輸線路上可以看出,若是理想狀況,線路沒有干擾時,

在發(fā)送側,可以形象理解為:

IN=IN+-IN-

在接收側,可以理解為:

IN+-IN-=OUT

所以:

OUT=IN

在實際線路傳輸中,線路存在干擾,并且同時出現(xiàn)在差分線對上,

在發(fā)送側,仍然是:

IN=IN+-IN-

線路傳輸干擾同時存在于差分對上,假設干擾為q,則接收則:

(IN++q)-(IN--q)=IN+-IN-=OUT

所以:

OUT=IN

噪聲被抑止掉。

上述可以形象理解差分方式抑止噪聲的能力。在實際芯片中,是在噪聲容限內(nèi),采用“比較”及“量化”來處理的。

LVDS接收器可以承受至少±1V的驅動器與接收器之間的地的電壓變化。由于LVDS驅動器典型的偏置電壓為+1.2V,地的電壓變化、驅動器偏置電壓以及輕度耦合到的噪聲之和,在接收器的輸入端相對于接收器的地是共模電壓。這個共模范圍是:+0.2V~+2.2V。建議接收器的輸入電壓范圍為:0V~+2.4V。

抑止共模噪聲是DS(差分信號)的共同特性,如RS485,RS422電平,采用差分平衡傳輸,由于其電平幅度大,更不容易受干擾,適合工業(yè)現(xiàn)場不太惡劣環(huán)境下通訊。