【導讀】晶體管的開關速度即由其開關時間來表征,開關時間越短,開關速度就越快。BJT的開關過程包含有開啟和關斷兩個過程,相應地就有開啟時間ton和關斷時間toff,晶體管的總開關時間就是ton與toff之和。

如何提高晶體管的開關速度?——可以從器件設計和使用技術兩個方面來加以考慮。

(1)晶體管的開關時間

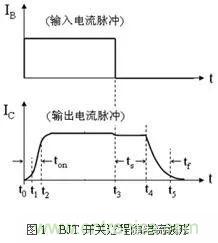

晶體管的開關波形如圖1所示。其中開啟過程又分為延遲和上升兩個過程,關斷過程又分為存儲和下降兩個過程,則晶體管總的開關時間共有4個:延遲時間td,上升時間tr,存儲時間ts和下降時間tf。

ton=td+tr

toff=ts+tf

在不考慮晶體管的管殼電容、布線電容等所引起的附加電容的影響時,晶體管的開關時間就主要決定于其本身的結構、材料和使用條件。

① 延遲時間td

延遲時間主要是對發射結和集電結勢壘電容充電的時間常數。因此,減短延遲時間的主要措施,從器件設計來說,有如:減小發射結和集電結的面積(以減小勢壘電容)和減小基極反向偏壓的大小(以使得發射結能夠盡快能進入正偏而開啟晶體管);而從晶體管使用來說,可以增大輸入基極電流脈沖的幅度,以加快對結電容的充電速度(但如果該基極電流太大,則將使晶體管在導通后的飽和深度增加,這反而又會增長存儲時間,所以需要適當選取)。

② 上升時間tr

上升導通時間是基區少子電荷積累到一定程度、導致晶體管達到臨界飽和(即使集電結0偏)時所需要的時間。因此,減短上升時間的主要措施,從器件設計來說有如:增長基區的少子壽命(以使少子積累加快),減小基區寬度和減小結面積(以減小臨界飽和時的基區少子電荷量),以及提高晶體管的特征頻率fT(以在基區盡快建立起一定的少子濃度梯度,使集電極電流達到飽和);而從晶體管使用來說,可以增大基極輸入電流脈沖的幅度,以加快向基區注入少子的速度(但基極電流也不能過大,否則將使存儲時間延長)。

③ 存儲時間ts

存儲時間就是晶體管從過飽和狀態(集電結正偏的狀態)退出到臨界飽和狀態(集電結0偏的狀態)所需要的時間,也就是基區和集電區中的過量存儲電荷消失的時間;。而這些過量少子存儲電荷的消失主要是依靠復合作用來完成,所以從器件設計來說,減短存儲時間的主要措施有如:在集電區摻Au等來減短集電區的少子壽命(以減少集電區的過量存儲電荷和加速過量存儲電荷的消失;但是基區少子壽命不能減得太短,否則會影響到電流放大系數),盡可能減小外延層厚度(以減少集電區的過量存儲電荷)。而從晶體管使用來說,減短存儲時間的主要措施有如:基極輸入電流脈沖的幅度不要過大(以避免晶體管飽和太深,使得過量存儲電荷減少),增大基極抽取電流(以加快過量存儲電荷的消失速度)。

④ 下降時間tf

下降時間的過程與上升時間的過程恰巧相反,即是讓臨界飽和時基區中的存儲電荷逐漸消失的一種過程。因此,為了減短下降時間,就應該減少存儲電荷(減小結面積、減小基區寬度)和加大基極抽取電流。

總之,為了減短晶體管的開關時間、提高開關速度,除了在器件設計上加以考慮之外,在晶體管使用上也可以作如下的考慮:a)增大基極驅動電流,可以減短延遲時間和上升時間,但使存儲時間有所增加;b)增大基極抽取電流,可以減短存儲時間和下降時間。

(2)晶體管的增速電容器

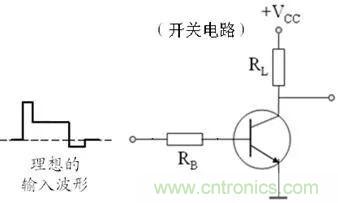

在BJT采用電壓驅動時,雖然減小基極外接電阻和增大基極反向電壓,可以增大抽取電流,這對于縮短存儲時間和下降時間都有一定的好處。但是,若基極外接電阻太小,則會增大輸入電流脈沖的幅度,將使器件的飽和程度加深而反而導致存儲時間延長;若基極反向電壓太大,又會使發射結反偏嚴重而增加延遲時間,所以需要全面地進行折中考慮。可以想見,為了通過增大基極驅動電流來減短延遲時間和上升時間的同時、又不要增長存儲時間和產生其它的副作用,理想的基極輸入電流波形應該是如圖2所示階梯波的形式,這樣的階梯波輸入即可克服上述矛盾,能夠達到提高開關速度的目的。

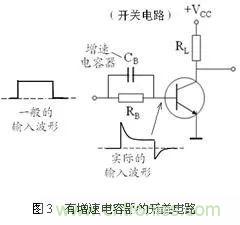

實際上,為了實現理想的基極電流波形,可以方便地采用如圖3所示的基極輸入回路(微分電路),圖中與基極電阻RB并聯的CB就稱為增速電容器。在基極輸入回路中增加一個增速電容器之后,雖然輸入的電流波形仍然是方波,但是通過增速電容器的作用之后,所得到的實際基極輸入電流波形就變得很接近于理想的基極電流波形了,于是就可以減短開關時間、提高開關速度。

推薦閱讀: