【導(dǎo)讀】作為可編程的邏輯器件,F(xiàn)PGA便于調(diào)試、修改、功耗低,能夠完成大量算法。在處理圖像和信號(hào)時(shí)平方根運(yùn)算被廣泛使用。在FPGA上利用VHDL和Verilog等編程語(yǔ)言進(jìn)行硬件設(shè)計(jì),存在仿真和校驗(yàn)效率低、算法復(fù)雜等問(wèn)題。而Python以其簡(jiǎn)單、功能強(qiáng)大的特點(diǎn)在此次設(shè)計(jì)中起到關(guān)鍵作用。

一、平方根實(shí)現(xiàn)

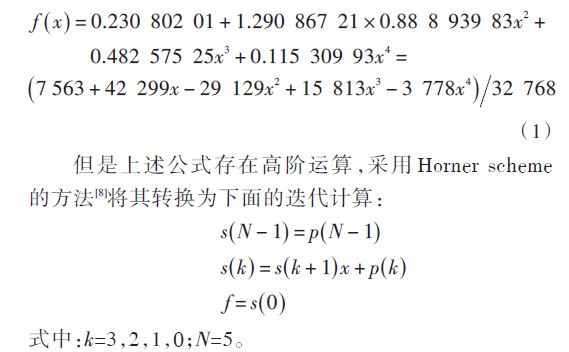

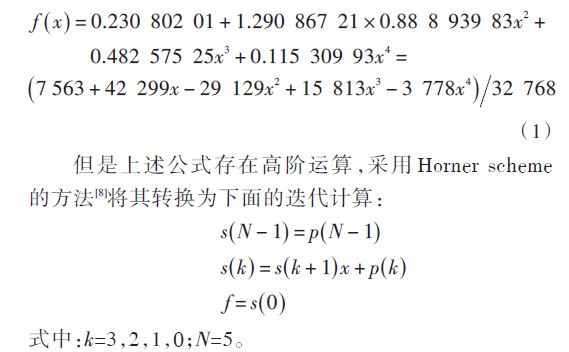

平方根的FPGA實(shí)現(xiàn)方法很多,有的算法為了減少片上資源的使用,邏輯實(shí)現(xiàn)上盡量避免使用乘法,比如CORDIC,逐位計(jì)算,non-restoring 等,現(xiàn)在FPGA上通常都有硬件乘法器,可采用迭代法和泰勒級(jí)數(shù)展開,本文采用泰勒級(jí)數(shù)展開的方法,級(jí)數(shù)采用5級(jí),系數(shù)采用3.15的定點(diǎn)表示形式,小數(shù)部分15位,整數(shù)部分2位為了保證后續(xù)計(jì)算結(jié)果不溢出,整個(gè)位寬為18位,計(jì)算公式如式(1)所示:

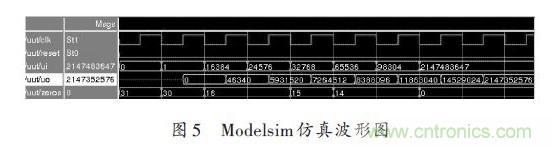

對(duì)于輸入x 位于(65 536,0]之間,由于數(shù)的范圍較大,通常進(jìn)行歸一化處理,采用的方法通過(guò)左移運(yùn)算去掉二進(jìn)制定點(diǎn)數(shù)的所有前導(dǎo)零,將輸入的數(shù)轉(zhuǎn)換為定點(diǎn)小數(shù)[0.5,1)之間,在完成平方根運(yùn)算之后,然后根據(jù)前導(dǎo)零個(gè)數(shù)的奇、偶性不同分別進(jìn)行去歸一化處理,原理如式(2)所示,將輸入數(shù)y 分為sx,s=2n,n 即為y 的二進(jìn)制前導(dǎo)零的個(gè)數(shù)。

整個(gè)過(guò)程的設(shè)計(jì)模塊如圖1所示。

二、定點(diǎn)數(shù)表示

通常在FPGA 上的運(yùn)算可以采用定點(diǎn)和浮點(diǎn)兩種方式來(lái)實(shí)現(xiàn),定點(diǎn)運(yùn)算和浮點(diǎn)運(yùn)算相比盡管數(shù)表示的范圍較小,設(shè)計(jì)較為復(fù)雜,但是速度較快,占用FPGA資源較小,本設(shè)計(jì)采用定點(diǎn)來(lái)完成。平方根的輸入為非負(fù)數(shù),包括符號(hào)位為定點(diǎn)32位輸入,其中高16位為整數(shù)部分,低15位為小數(shù)部分,可以直接計(jì)算的平方根范圍為(65 536,0],結(jié)果采用32位輸出,最高位為符號(hào)位,接著的高8位為整數(shù)部分,低23位為小數(shù)部分。

三、實(shí)驗(yàn)環(huán)境

采用MyHDL 0.8,采用GTKWAVE 查看仿真波形,F(xiàn)PGA 器件采用Altera公司CycloneⅡ 2C35F672C6,編譯綜合采用Quartus 12.1sp1 webpack.

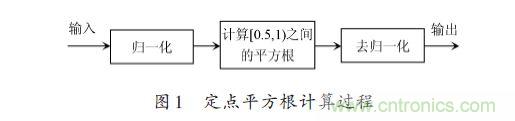

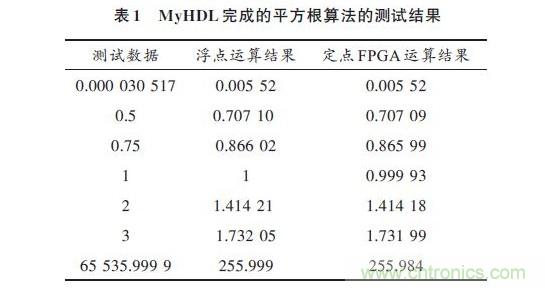

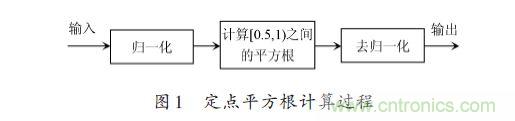

四、Python軟硬件協(xié)同設(shè)計(jì)

基于Python 的軟硬件協(xié)同設(shè)計(jì)的過(guò)程如圖2 所示,由于本設(shè)計(jì)最終要在硬件上實(shí)現(xiàn),在設(shè)計(jì)時(shí)Python的硬件設(shè)計(jì)部分采用MyHDL 可綜合子集,最后使用MyHDL的toVerilog()函數(shù)將MyHDL設(shè)計(jì)自動(dòng)轉(zhuǎn)換為相應(yīng)的Verilog 代碼,由于MyHDL 支持與Verilog 混合仿真,設(shè)計(jì)時(shí)的測(cè)試平臺(tái)可以重用,仿真速度和設(shè)計(jì)效率大大提高。在完成基于Python軟硬件設(shè)計(jì)并仿真正確之后,就可以回到進(jìn)行傳統(tǒng)的FPGA 設(shè)計(jì)流程,進(jìn)行后續(xù)的下載,綜合和測(cè)試工作。

[page]

五、仿真波形

在設(shè)計(jì)過(guò)程中生成的VCD仿真波形可以隨時(shí)采用GTKWAVE 查看,可以便于校驗(yàn)設(shè)計(jì)是否正確,最終完成的仿真波形如圖3所示。

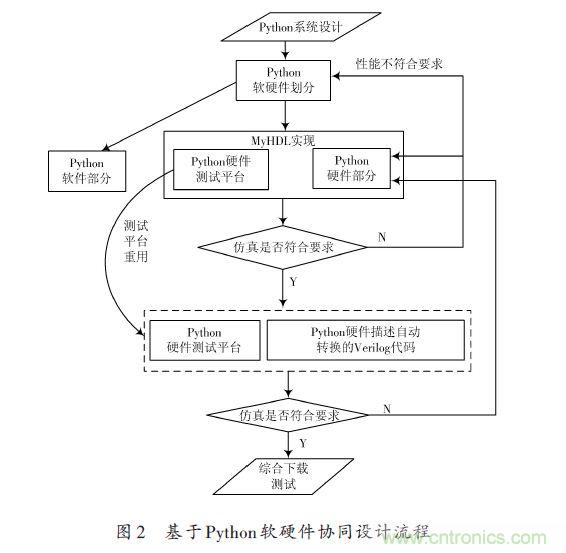

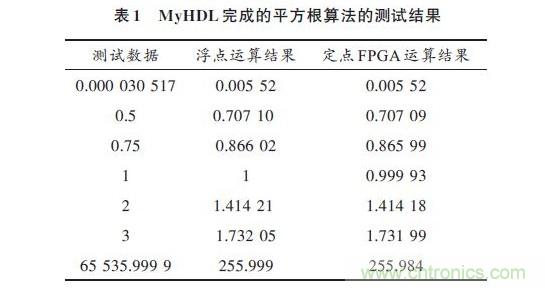

六、測(cè)試數(shù)據(jù),精度及誤差

由于整個(gè)過(guò)程采用Python設(shè)計(jì),Python存在大量的軟件包可以使用,平方根完成的測(cè)試數(shù)據(jù)結(jié)果如表1所示,采用基于Python 的繪圖包matplotlib 繪制的當(dāng)x 在[0.5,1.0]之間時(shí)的平方根誤差如圖4所示。

七、綜合結(jié)果

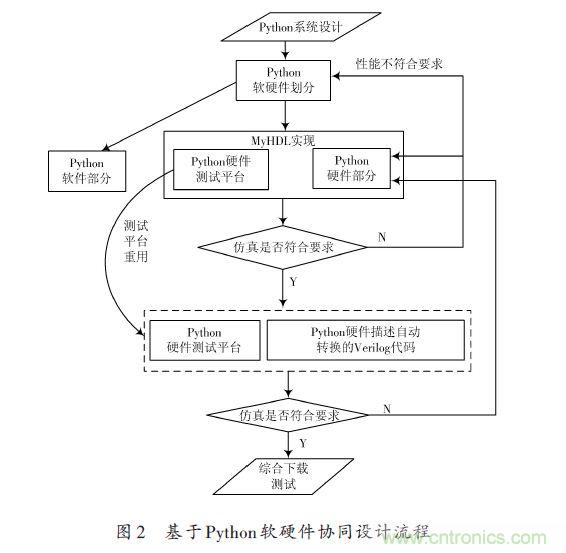

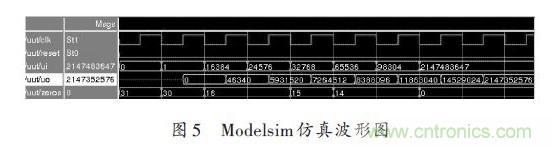

在上面仿真校驗(yàn)符合設(shè)計(jì)要求后,將Python自動(dòng)轉(zhuǎn)換為Verilog描述,采用Quartus編譯綜合,并使用Model-sim仿真的波形如圖5所示,與圖3的Python環(huán)境下仿真波形相似,由此可見采用Python的軟硬件協(xié)同設(shè)計(jì)方法能有效地進(jìn)行FPGA 設(shè)計(jì)。綜合后FPGA 資源使用情況:LE共1 506個(gè),寄存器64個(gè),嵌入式9位硬件乘法器10個(gè)。