【導讀】無論是設計測試和測量設備還是汽車激光雷達模擬前端(AFE),使用現代高速數據轉換器的硬件設計人員都面臨高頻輸入、輸出、時鐘速率和數字接口的嚴峻挑戰。問題可能包括與您的現場可編程門陣列(FPGA)相連、確信您的首個設計通道將起作用或確定在構建系統之前如何對系統進行最佳建模。

本文中將仔細研究這些挑戰。

快速的系統開發

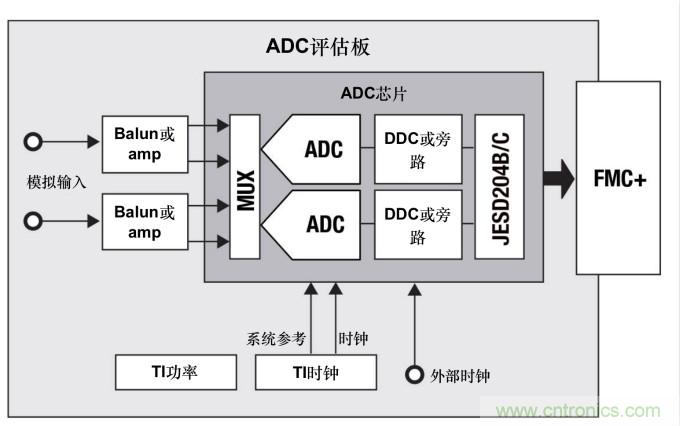

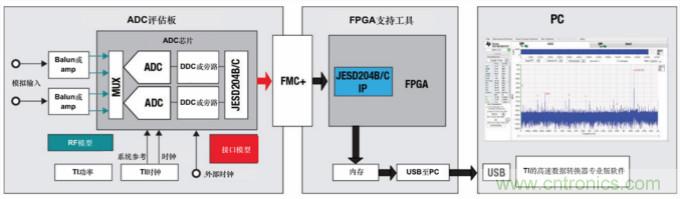

開始新的硬件設計之前,工程師經常會在自己的測試臺上評估最重要的芯片。一旦獲得了運行典型評估板所需的設備,組件評估通常會在理想情況的電源和信號源下進行。TI大多數情況下會提供車載電源和時鐘,以便您可使用最少的測試臺設備以及如圖1所示設置的更實際的電源和信號源來運行電路板。

圖1:典型的ADC評估板

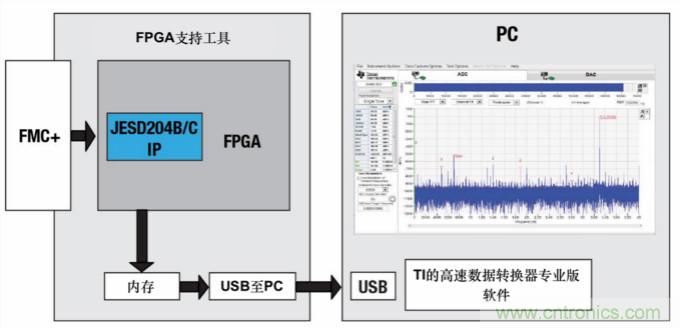

驗證性能后,可將更完整的評估板的示意圖和布局作為那一部分子系統的參考設計部分子。我們的數據采集和模式生成工具支持CMOS、LVDS和JESD204,并附帶操作它們所需的軟件。為您的高速數據轉換器使用評估板用戶指南,可在不到10分鐘的時間內啟動并運行大多數評估板。參見圖2。

圖2:TI的數據采集和模式生成的硬件和軟件

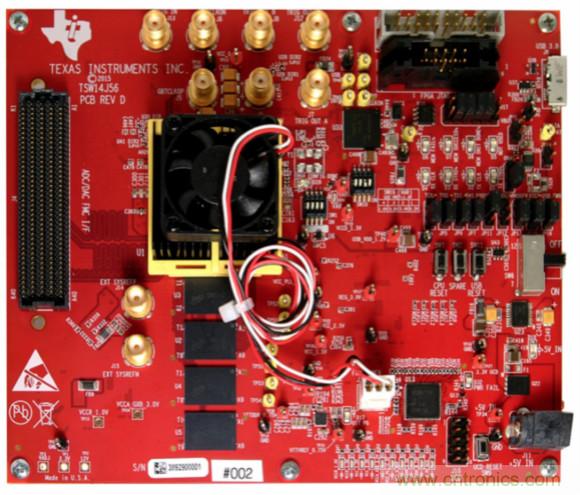

隨著系統變得越來越復雜,您可能需要評估更廣范圍的用例。此時你可能會需要一塊評估板。如果您的評估需求變得復雜,則可使用Python、MATLAB、LabVIEW或C ++軟件通過設備評估板、采集卡解決方案和測試臺設備直接與設備通信。我們支持板的一些很好的示例包括用于LVDS/CMOS的TSW1400EVM以及用于支持JESD204B串行器-解串器(SerDes)協議設備的TSW14J56EVM,如圖3所示。

圖3:TI的用于JESD204B數據采集或模式生成的TSW14J56EVM

TI還支持單臺PC上的有多評估模塊原型的完整系統級模型。例如,通過將KCU105或VCU118等Xilinx FPGA開發套件連接到多個模擬-數字轉換器(ADC)或數字-模擬轉換器(DAC),可同時測試發送和接收通道。

在線CTA:

加速從概念到原型的設計。

探索我們的JESD204快速設計IP,以簡化FPGA集成并縮短總體開發時間。

FPGA連通性以及JESD204B和JESD204C

您可能要解決的最大問題之一是如何在FPGA中獲取數據。盡管LVDS和CMOS是簡易接口,但它們在設備上每個管腳上支持的速度極其有限。隨著更新型的高速數據轉換器更普遍地支持> 1 GSPS的輸入或輸出速率,這些接口要么失去市場,要么使設計變得復雜。

為微電子行業制定開放標準的JEDEC創建了JESD204,通過支持超過12.5 Gbps的差分對通道速率來解決此問題。但盡管JESD204最大限度地減少了管腳數量,但它通過對并行數據進行編碼和串行化或反序列化和解碼增加了接口復雜性。

到目前為止,您不得不主要依靠JESD204知識產權(IP)塊和FPGA供應商提供的支持。盡管這些IP塊可很好地工作,但它們以支持任意配置的任何設備的方式提供。這意味著很難為您的特定用例進行了解和配置。您需要花費大量精力自己設計IP,或從第三方IP提供商那里尋求IP。但如果出現問題,第三方IP將需要在實現方面提供幫助和支持。

TI自有的JESD204快速設計IP可針對您的FPGA平臺、數據轉換器和JESD204模式進行預配置和優化。我們的IP需要更少的FPGA資源,同時還可針對每種特定用途進行定制。另一個優點是實現JESD204鏈接僅需數小時或數天,而非數周或數月的時間。

設備模型

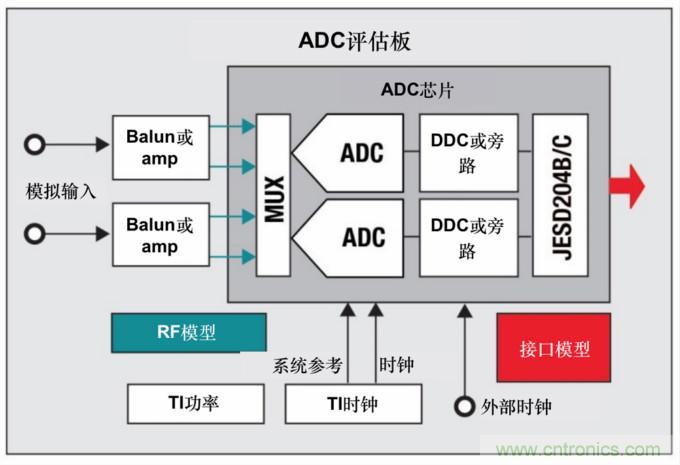

隨著直接射頻(RF)采樣和超快SerDes與高速數據轉換器的結合變得越來越普遍,對RF和信號完整性進行建模的能力已成為成功通過首次設計的必要條件。傳統上講,大多數供應商僅為S參數模型中的ADC提供輸入阻抗信息,但TI的ADC12DJ3200、ADC12DJ5200RF和ADC12QJ1600-Q1高頻輸入器件的目標是高達8 GHz的采樣頻率,現在具有包含阻抗和頻率響應信息的S參數模型。

使用此新模型,您可模擬預期的設備行為并優化阻抗匹配。TI的策略是在支持極高的輸入和輸出頻率的設備上提供這些模型,而阻抗匹配和實現所需的頻率響應則更具挑戰性。

在數據轉換器的數字接口側,輸入/輸出緩沖區信息規范(IBIS)是一種通用模型,可為CMOS和LVDS管腳提供物理層信息以及DC和AC類型的行為。對于大多數使用高速JESD204 SerDes的新型數據轉換器,這些模型已改進為IBIS-算法建模接口(AMI),其中包括有助于應用均衡和預加重或后加重的有用信息。IBIS-AMI提供您所需的建模功能,使您首次即可正確使用電路板,同時實現良好的誤碼率、信號完整性和穩健的數據鏈路。圖4所示為RF(綠色)和數字接口(藍色)模型。

圖4:接口建模

結論

無論您使用高速數據轉換器進行設計已有一段時間,還是對高速設計還不太熟悉,都不用擔心,因為TI正設計易于使用的高速數據轉換器。我們構建了一個可簡化所有工作的完整開發環境,如圖5所示。

利用可輕松實現FPGA集成的現成IP、精確的RF系統模型以及市場上穩健的一組靈活、可擴展和可自動化的評估模塊,您可縮短幾個月的固件開發時間、減少昂貴的設計周期并加快從概念到原型的高速設計。

圖5:典型的高速模擬-數字轉換器(ADC)評估環境

推薦閱讀: