【導讀】該文將討論晶振電路設計方案,并解釋電路中的各個元器件的具體作用,并且在元器件數值的選擇上提供指導。最后,就消除晶振不穩定和起振問題,最后文章還將給出了一些建議措施。

1 晶振的等效電氣特性

(1) 概念

[1] 晶片,石英晶體或晶體、晶振、石英晶體諧振器

從一塊石英晶體上按一定方位角切下薄片。

[2] 晶體振蕩器

在封裝內部添加IC組成振蕩電路的晶體元件稱為晶體振蕩器。

(2) 晶振等效電路

圖1. 晶振的等效電路

圖1展示了晶振等效的電路。R是ESR串聯等效阻抗,L和C分別是晶振等效電感和等效電容。Cp是晶振的伴身電容,其極性取決于晶振的極性。

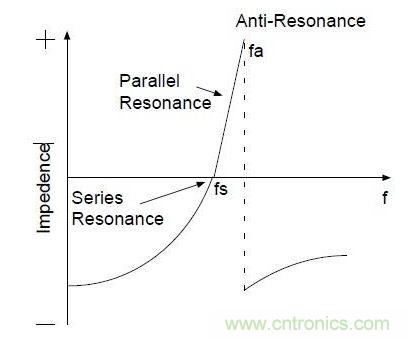

圖2是晶振的電抗頻譜線。

圖2. 晶振的電抗頻譜線

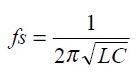

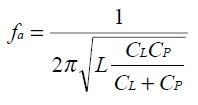

根據圖 2,當晶振工作在串聯諧振狀態下時,電路就似一個純電阻電路,感抗等于容抗(XL=XC)。串聯諧振的頻率為:

當晶振工作在并聯諧振模式時,晶振表現為感性。該模式的工作頻率由晶振的負載決定。對于并聯諧振狀態的晶振,晶振制造商應該指定負載電容CL。在這種模式下,振動頻率由下式給出

在并聯諧振模式下,電抗線中fs到fa的斜線區域內,通過調整晶振的負載,如圖2,晶振都可以振蕩起來。

2 晶振電路的設計

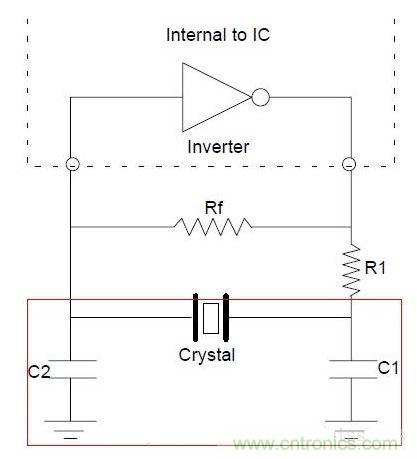

圖3所示為推薦的晶振振蕩電路圖。這樣的組成可以使晶振處于并聯諧振模式。反相器在芯片內體現為一個AB型放大器,它將輸入的電量相移大約180°后輸出;并且由晶振,R1,C1和C2組成的π型網絡產生另外180°的相移。所以整個環路的相移為360°。這滿足了保持振蕩的一個條件。其它的條件,比如正確起振和保持振蕩,則要求閉環增益應≥1。

圖3. 晶振振蕩器設計電路

反相器附近的電阻Rf產生負反饋,它將反相器設定在中間補償區附近,使反相器工作在高增益線性區域。電阻值很高,范圍通常在500KΩ ~2MΩ內。

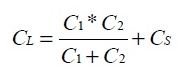

圖示的C1,C2就是為晶振工作在并聯諧振狀態下得到加載電容CL的電容。關于最優的加載電容CL的計算公式為:

這里CS是PCB的漂移電容(stray capacitance),用于計算目的時,典型值為5pf。現在C1和C2選擇出來滿足上面等式。通常選擇的C1和C2是大致相等的。C1和/或C2的數值較大,這提高了頻率的穩定性,但減小了環路增益,可能引發起振問題。

R1是驅動限流電阻,主要功能是限制反相器輸出,這樣晶振不會被過驅動(over driven)。R1、C1組構成分壓電路,這些元器件的數值是以這樣的方式進行計算的:反相器的輸出接近rail-to-rail值,輸入到晶振的信號是rail-to-rail的60%,通常實際是令R1的電阻值和的C1容抗值相等,即R1 ≈ XC1。這使晶振只取得反相器輸出信號的一半。要一直保證晶振消耗的功率在廠商說明書規定范圍內。過驅動會損壞晶振。

理想情況下,反相器提供180°相移。但是,反相器的內在延遲會產生額外相移,而這個額外相移與內在延遲成比例。為保證環路全相移為n360°,π 型網絡應根據反相器的延遲情況,提供小于180°的相移。R1的調整可以滿足這一點。使用固定大小的C1和C2,閉環增益和相位可隨R1變化。如果上述兩個條件均得到了滿足,在一些應用中,R1可以忽略掉。

一些芯片內置了全部這些外部器件(Rf, R1, C1, and C2),因此消除了電路設計師的煩惱。這種情況下,只要把晶振連接在XTAL和XTAL引腳上即可。

提示:

選擇ESR小的晶振,有利于解決起振問題。較小的ESR可以增加環路增益。

在PCB板上縮短線路可以減小漂移電容。這也有利于解決晶振起振和振蕩頻率的問題。

在工作的溫度下和工作的電壓范圍內經常性測試一下電路,以確保晶振起振和持續振蕩。必要的時候調整元器件的數值。

為了取得最好效果,晶振的設計,用至少0.4 Vdd(峰峰值)的電平驅動時鐘反相器。調節晶振不能滿足要求。為了獲得進一步的設計協助,請聯系晶振制造商。

為了優化R1,我們推薦先計算C1和C2(前面已經解釋過如何計算)。將R1替換成電位計,將其初始值設置到大約XC1。如果需要,調節電位計的設置,直到晶振起振并在穩態條件下保持振蕩。

【推薦閱讀】

解析三種嵌入式系統控制電路設計

測量儀器中的各種波形抽取方式

低功耗溫度補償式電橋信號調理器和驅動器電路

無電池式低功耗藍牙Beacon:采用能量采集技術的BLE

電壓模式、遲滯和基于遲滯:選擇哪一種呢?