【導(dǎo)讀】SPI英文全稱Serial Peripheral Interface,SPI串行外圍接口是具有通信可靠、速度快、電路簡單等特點的三線同步串行全雙工通信接口。SPI接口在EEPROM存儲器、LCD模塊、數(shù)據(jù)輸入輸出設(shè)備、FLASH等器件中廣泛應(yīng)用。目前的單片機都將SPI接口控制器集成于于內(nèi)部,更有利于軟件的運行,操作更加方便。

由于SPI系統(tǒng)總線一共只需3~4位數(shù)據(jù)線和控制線即可實現(xiàn)與具有SPI總線接口功能的各種I/O器件進行接口,而擴展并行總線則需要8根數(shù)據(jù)線、8—16位地址線、2~3位控制線,因此,采用SPI總線接口可以簡化電路設(shè)計,節(jié)省很多常規(guī)電路中的接口器件和I/0口線,提高設(shè)計的可靠性,使用 SPI總線可以增加應(yīng)用系統(tǒng)接口器件的種類,提高應(yīng)用系統(tǒng)的性能。

1、設(shè)計方案

通過深入分析SPI的四種傳輸協(xié)議可以發(fā)現(xiàn),根據(jù)一種協(xié)議,只要對串行同步時鐘進行轉(zhuǎn)換,就能得到其余的三種協(xié)議。為了簡化設(shè)計,規(guī)定如果要連續(xù)傳輸多個數(shù)據(jù),在兩個數(shù)據(jù)傳輸之問插入一個串行時鐘的空閑等待,這樣狀態(tài)機只需兩種狀態(tài)(空閑和工作)就能正確工作。相比其它設(shè)計,在基本不降低性能的前提下,思路比較精煉、清晰,能夠大大縮短寫代碼的時間,降低出錯率。

此SPI模塊有兩種工作方式:查詢方式和DMA方式。查詢方式通過處理器核監(jiān)視SPI的狀態(tài)寄存器來獲取其所處的狀態(tài),從而決定下一步動作。DMA方式由DMA模塊控制數(shù)據(jù)在內(nèi)存和SPI間的交換,而不需要處理器核的參與,有效提高了總線利用率。

外部MCU可以通過和內(nèi)部MCU通訊的方式,把從模式的SPI配置成可以解析命令的模式,這樣外部主模式的SPI可以在SSN低電平的時候連續(xù)傳輸多位數(shù)據(jù),在下降沿的第一個數(shù)據(jù)被認(rèn)為是命令。從模式的SPI可以解析這些命令然后做相應(yīng)的操作。這些操作主要包括,清除接收FIFO或者發(fā)送 FIFO中的數(shù)據(jù),選擇MCU或者DMA來作為數(shù)據(jù)交互的對象等,可以大大節(jié)省和MCU交互所需要的帶寬。

作為主要組成部分的寄存器控制模塊和SPI核心模塊采用同步電路設(shè)計,它們之間的通訊采用異步電路設(shè)計。這些主要是考慮到SPI的帶寬通過MCU的控制是可調(diào)的。SPI核心部分的時鐘頻率可調(diào),可實現(xiàn)多種帶寬,增加了本設(shè)計SPI的靈活性。

2、內(nèi)部總線接口

在本設(shè)計中,內(nèi)部總線接口采用的是AMBA總線3.0協(xié)議,具有較好的可移植性和可復(fù)用性。SPI是APB總線上的Slave模塊。APB總線的時序完全遵照(ABMA Specification)(Rev 3.0)。因此此SPI模塊支持3種DMA操作,除了標(biāo)準(zhǔn)信號線外,還有3根與DMA模塊連接的中斷請求信號線。

3、SPI總線接口及時序

SPI串行接口使用4條線可與多種標(biāo)準(zhǔn)外圍器件直接接口:串行時鐘線SCLK,主機輸入/從機輸出數(shù)據(jù)線MISO,主機輸出/從機輸人數(shù)據(jù)線MOSI和低電平有效的從機選擇線SSN。SCLK是主機時鐘線,為MISO數(shù)據(jù)的發(fā)送和接收提供同步時鐘信號。在正常工作的時候,主機的4個引腳應(yīng)和從機對應(yīng)的4個引腳分別相連。

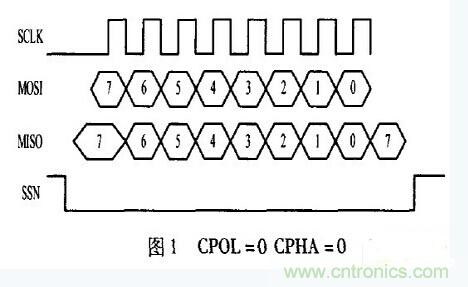

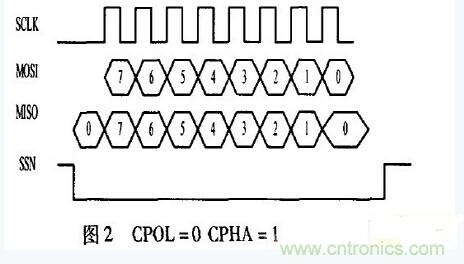

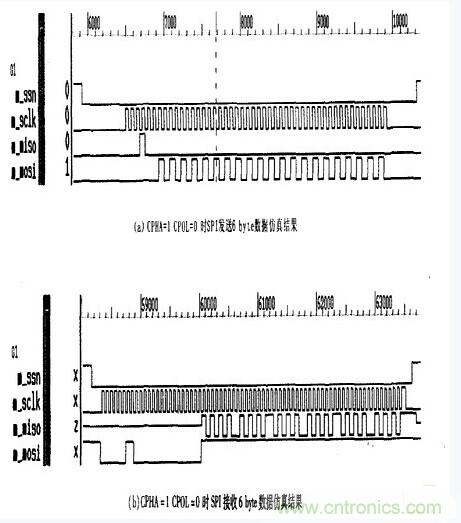

SPI模塊為了和外設(shè)進行數(shù)據(jù)交換,根據(jù)外設(shè)的工作要求,其輸出串行同步時鐘的極性和相位可以進行配置,時鐘的極性(CPOL)對傳輸?shù)膮f(xié)議沒有重大影響。如果CPOL=0,串行同步時鐘的空閑狀態(tài)為低電平;相反,如果CPOL=l,串行同步時鐘的空閑狀態(tài)為高電平。時鐘相位(CPHA)能夠配置用于選擇兩種不同的傳輸協(xié)議之一進行數(shù)據(jù)傳輸。

如果CPHA=0,在串行同步時鐘的第一個跳變沿(上升或下降)數(shù)據(jù)被采樣;如果CPHA=1,在串行同步時鐘的第二個跳變沿(上升或下降)數(shù)據(jù)被采樣。SPI主模塊和與之通信的外設(shè)時鐘相位和極性應(yīng)該一致。SPI接口時序如圖1、圖2所示。

圖1:CPOL=0 CPHA =0

圖2:CPOL=0 CPHA=1

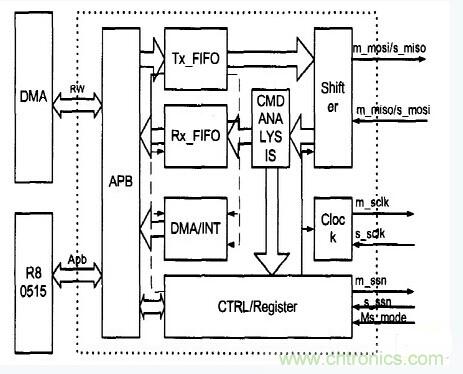

4、模塊劃分

根據(jù)功能定義及SPI的工作原理,將整個SPI IP劃分為8個子模塊:APB接口模塊、時鐘分頻模塊、發(fā)送數(shù)據(jù)FIFO模塊、接收數(shù)據(jù)FIFO模塊、寄存器控制模塊、命令解析模塊、中斷處理模塊及發(fā)送接收數(shù)據(jù)模塊。整個SPI模塊劃分結(jié)構(gòu)圖如圖3所示。

圖3:數(shù)據(jù)傳輸結(jié)構(gòu)

在這些模塊中,Tx—FIFO和Rx—FIFO用來做接收發(fā)送數(shù)據(jù)的FIFO。DMA/INT是中斷控制模塊,通知MCU或者DMA發(fā)送或者接收數(shù)據(jù)的FIFO。CMD ANALYSIS模塊用來解析在從模式下Host發(fā)過來的命令。CTRl/Register用來放置寄存器,供MCU讀寫配置SPI的各種參數(shù)。 Shifter用來做串并轉(zhuǎn)換,收發(fā)送數(shù)據(jù)。Clock模塊用來產(chǎn)生主模式下時鐘。

[page]

5、SPI的工作模式

5、SPI的工作模式

SPI有兩種工作模式,可以通過外部引腳跳線的方式來切換。

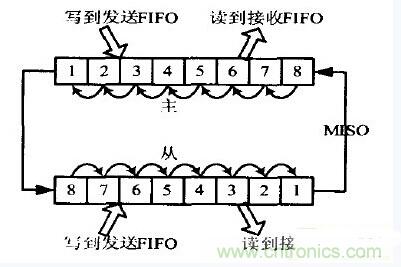

主模式:發(fā)送和接收可以同時工作在主模式下。主模式的顯著特征是不論是發(fā)送還是接收始終有SCLK信號,發(fā)送操作是由向發(fā)送FIFO中寫數(shù)據(jù)而觸發(fā)的。在主模式下,時鐘信號的1次作用對應(yīng)一位數(shù)據(jù)的發(fā)送(MOSI)和另一位數(shù)據(jù)的接收(MISO)。

如圖4所示,在主片中數(shù)據(jù)從移位寄存器中自右向左發(fā)出送到從片(MOSI),同時從片中的數(shù)據(jù)自左向右發(fā)到主片(MISO),經(jīng)過8位時鐘周期完成1個字節(jié)的發(fā)送。輸入字節(jié)保留在移位寄存器中,此時SPI INT FLAG位自動置位(如果有中斷設(shè)置,則產(chǎn)生中斷),移位寄存器的數(shù)據(jù)將被鎖存到接收FIFO中,此后對接收FIFO的讀操作將把數(shù)據(jù)讀出。

從模式:發(fā)送和接收同時工作在從模式下。從模式的顯著特征是:不論是發(fā)送還是接收始終必須在SCLK信號作用下進行,并且SSN信號必須有效。

當(dāng)SSN信號無效時,數(shù)據(jù)的發(fā)送無法進行并且輸入的數(shù)據(jù)視為無效。數(shù)據(jù)的發(fā)送和接收過程見圖3所示,與主模式下基本相似,只是移位寄存器的數(shù)據(jù)移出和輸入方向與之相反。

圖4:主片和從片發(fā)送和接收操作

6、SPI的電路實現(xiàn)

為了保證RTL代碼的正確性,對IP的功能進行全面的仿真驗證。仿真包括RTL級和門級仿真驗證。RTL級仿真是將代碼文件調(diào)入硬件描述語言的仿真軟件進行功能仿真,門級仿真包括布局布線前和布局布線后仿真。布局布線后仿真,獲得精確的時延參數(shù)。將RTL級代碼轉(zhuǎn)換成門級網(wǎng)表,0.13um工藝標(biāo)準(zhǔn)單元庫。

在傳統(tǒng)的設(shè)計流程中進行功能驗證,首先需要通過寫測試矢量的方式給需要進行功能測試的模塊加激勵,然后通過觀察模塊的輸出結(jié)果,判斷模塊的功能是否正確。但是在寫測試矢量時,測試工程師是在自己對模塊功能理解的基礎(chǔ)上進行的。這樣就存在一個問題,測試矢量對模塊的激勵有可能是不完備的,還有可能是錯誤的,但測試矢量的激勵并沒有使錯誤體現(xiàn)出來;也有可能模塊的功能是正確的,誤報錯誤使驗證過程變得非常低效。為避免以上問題,對本設(shè)計模塊的功能驗證中,采用系統(tǒng)級驗證環(huán)境。該環(huán)境由IP總線、驅(qū)動器、監(jiān)視器、外部模塊和協(xié)調(diào)它們工作的腳本組成。組成系統(tǒng)的各模塊可以按需要加人環(huán)境。每次驗證過程就是相應(yīng)的激勵作用于環(huán)境的過程。驗證結(jié)果由環(huán)境產(chǎn)生、檢驗和輸出。以保證測試矢量的完備性和正確性。

該驗證環(huán)境在LINUX操作系統(tǒng)下,仿真器采用Cadence公司的Nc—verilog,支持C/C++、Verilog和VHDL協(xié)同仿真,可以直接把SPI模塊掛在驗證環(huán)境中,通過Verilog的$readmemh任務(wù)讀入軟件激勵進行驗證。在系統(tǒng)時鐘為36MHz的情況下,圖5(a)給出了CPOL=0,CPHA=1時,發(fā)送6位數(shù)據(jù)的仿真結(jié)果。圖5(b)給出了在CPOL=0,CPHA=0的情況下,接收6位數(shù)據(jù)的仿真結(jié)果。

圖5:仿真結(jié)果

這兩個仿真結(jié)果說明本設(shè)計完全支持4種SPI傳輸協(xié)議,而且能夠以最大的速率無縫傳輸數(shù)據(jù)。

結(jié)語:在本次設(shè)計中,SPI作為IP核嵌入監(jiān)控系統(tǒng)SOC芯片中,芯片經(jīng)測驗,指標(biāo)符合設(shè)計要求。芯片中的SPI在進行板級測試后能夠支持四種傳輸協(xié)議,能夠在1秒鐘內(nèi)抓圖,回顯15幀圖像,工作效率達到18Mbps.是業(yè)界領(lǐng)先水平。然而此次設(shè)計也有缺陷之處,設(shè)計過程中沒有做過數(shù)據(jù)校驗,隨著技術(shù)提升,設(shè)計過程中增加CRC校驗?zāi)軌蛟黾訑?shù)據(jù)的正確性,使系統(tǒng)的效率得到提升。

相關(guān)閱讀:

SPI總線的特點、工作方式及常見錯誤解答

集成5GHz JESD204B串行接口的8通道超聲接收器

CM6100:CMD面向高速串行接口的低電容靜電放電保護設(shè)備

相關(guān)閱讀:

SPI總線的特點、工作方式及常見錯誤解答

集成5GHz JESD204B串行接口的8通道超聲接收器

CM6100:CMD面向高速串行接口的低電容靜電放電保護設(shè)備