【導讀】明導近日發布一份題為《鰭式場效晶體管寄生提取的復雜性》的研究報告。鰭式場效晶體管的推出標志著 CMOS 晶體管首次被看作是真正的三維器件。由于源漏區以及與其周圍連接的三維結構方式,導致了復雜性和不確定性。

Mentor Graphics近日發布一份題為《鰭式場效晶體管寄生提取的復雜性》的研究報告。中文版的報告全文可在 Mentor Graphics 的官方網站閱讀和下載:[ http://mentorg.com.cn/aboutus/view.php?id=231 ]。

圖1:Carey Robertson

作者:Carey Robertson,產品營銷、電路布局驗證和參數提取總監,Design to Silicon部門

Carey Robertson 是明導產品營銷總監,負責 Calibre PERC、LVS 和提取產品的營銷活動。他已在明導任職15年,擔任過各種產品和技術營銷職位。加盟明導之前,Carey 是迪吉多 (Digital Equipment Corp.) 的設計工程師,致力于微處理器設計。Carey 持有斯坦福大學 (Stanford University) 學士學位和加州大學伯克利分校 (UC Berkeley) 碩士學位。

鰭式場效晶體管(簡稱 finFET)的推出標志著 CMOS 晶體管首次被看作是真正的三維器件。由于源漏區以及與其周圍連接的三維結構方式(包括本地互連和接觸通孔),導致了復雜性和不確定性。

結果,器件建模不得不快速改進。UC Berkeley Device Group 的 BSIM Group開發出了一種名為BSIM-CMG(通用多柵極)的模型,用以表示存在于 finFET內部的電阻和電容。為了幫助緩解有關向finFET工藝轉變的擔憂,晶圓廠做了非常大的努力來提供器件和寄生精度數據,以及保存用于先前工藝的使用模型。

雖然我們有BSIM-CMG作為表示finFET設計參數的通用方式,但各個晶圓廠會增加或減少標準模型的組件,以便能夠更準確地代表其周圍的寄生效應。這種定制化受到多方面的推動, 包括各家晶圓廠使用各自的器件和寄生參數模型來與硅驗證結果匹配,以及使用電子設計自動化(EDA)工具來預測硅片上的結果。

此外,在高級工藝節點,晶圓廠希望他們的工藝、他們使用科學的場解算器(field solver )為這些工藝建立的“黃金”模型以及EDA廠商開發并且被設計人員用于該領域的提取工具的輸出結果之間擁有更緊密的聯系。在28納米節點,晶圓廠希望商用提取工具的誤差率保持在標準模型的5-10%以內。對于 finFET 工藝,晶圓廠要求平均準確度誤差保持在標準模型的2%以內,三西格瑪標準偏差僅為6-7%。

由于FinFET相互作用的復雜性,要想滿足晶圓廠對于EDA廠商的寄生提取工具和晶圓廠的標準模型結果一致性的要求,三維場解算器(3d field solver)必不可少。設計人員將首次能夠看到場解算器(field solver)結果,而這直到目前為止主要用于工藝特性鑒定,而非設計。所幸的是,該使用模型在進行寄生提取時不會發生變化,因為這些工具將自動在場解算器和啟發式方法之間轉換。

傳統上來說,場解算器(field solver)用于生產是不切實際的,因為它們需要太多的運算時間(也就是太慢)。在明導,我們開發出了Calibre“xACT3D”提取工具來解決這一問題。由于采用自適應網格技術來加速計算,該工具的速度要快上一個數量級或更多。它還擁有一個可擴展架構,能在現代化的計算環境中充分利用多個 CPU。因此,它能夠輕松的在一個32位CPU的機器上對一個版圖設計執行場解算器(field solver)計算方案,這些版圖設計包括小到一些小的單元(cell),大到擁有數百萬個晶體管的大模塊。

[page]

然而,對于全芯片而言,我們需要處理數十億晶體管的設計,還包括頂層的數千萬條導線(nets)。從周轉時間角度來看,僅僅使用快速場解算器是不切實際的。我們需要智能技巧和啟發式方法,首先針對復雜結構運用場解算器(field solver)技巧,然后再針對普通的幾何圖形改用查找表的方式。對高層次中的繞線轉換到查找表法是可行的,因為在布線網格中進行電場建模與在之前節點中看到的相似。事實上,第一代 finFET器件使用的是晶圓廠在平面工藝中采用的20納米互連法。

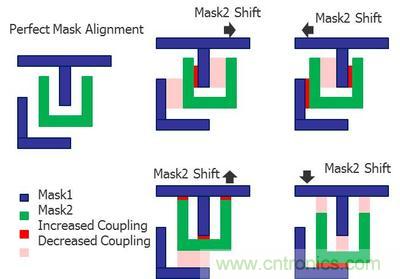

圖2:雙重成像(DP)的光罩可能存在的未對準情況要求設計人員評估更多寄生參數提取的corners,以驗證集成電路的時間選擇和性能。

考慮頂級互連提取時,我們需要更高效的計算方法,因為必須計算的寄生參數有所增加。此外,鑒于雙重成像(DP)和多重成像(MP)在制造中(20納米節點起步)發揮越來越重要的作用,互連corners的數量也將顯著增多。在28納米節點,可能存在5個互連corners,但在16納米節點,我們會看到11至15個corners。應對計算需求增加的一個傳統方法是使用更多CPU,并提升計算機core運算的可擴展性。我們正在這樣做,但我們還在執行先進的multi-corner分析技術,以實現更高效的計算。過去,我們估計每增加一個corner,運行時間將增加一倍(與單個corner相比)。現在,我們可以并行處理多個corners,使每增加一個corner而增加的總體周轉時間僅為10%。這意味著15個corners現在所需的運行時間僅為單個corner的2.5倍。通過采用先進的multi-corner分析以及利用更多的 CPU之間的平衡,我們可以使設計人員的周轉時間與28納米或20納米一樣甚至更短。

最近向finFET工藝的快速轉變給EDA 行業帶來了挑戰,要求該行業真正快速地拿出應對復雜新問題的有效解決方案。還有更多工作要做,但可以說的是,與之前工藝節點開發過程中的同一階段相比,我們現在在finFET工藝上擁有更多的EDA工具和晶圓廠的硅驗證之間的對比數據。