中心議題:

- 板上高速信號(hào)分析

- 印制板信號(hào)完整性整體設(shè)計(jì)

- 時(shí)鐘信號(hào)阻抗匹配

信號(hào)完整性問(wèn)題是高速PCB設(shè)計(jì)者必需面對(duì)的問(wèn)題。阻抗匹配、合理端接、正確拓?fù)浣Y(jié)構(gòu)解決信號(hào)完整性問(wèn)題的關(guān)鍵。傳輸線(xiàn)上信號(hào)的傳輸速度是有限的,信號(hào)線(xiàn)的布線(xiàn)長(zhǎng)度產(chǎn)生的信號(hào)傳輸延時(shí)會(huì)對(duì)信號(hào)的時(shí)序關(guān)系產(chǎn)生影響,所以PCB上的高速信號(hào)的長(zhǎng)度以及延時(shí)要仔細(xì)計(jì)算和分析。

運(yùn)用信號(hào)完整性分析工具進(jìn)行布線(xiàn)前后的仿真對(duì)于保證信號(hào)完整性和縮短設(shè)計(jì)周期是非常必要的。在PCB板子已焊接加工完畢后才發(fā)現(xiàn)信號(hào)質(zhì)量問(wèn)題和時(shí)序問(wèn)題,是經(jīng)費(fèi)和產(chǎn)品研制時(shí)間的浪費(fèi)。

1板上高速信號(hào)分析

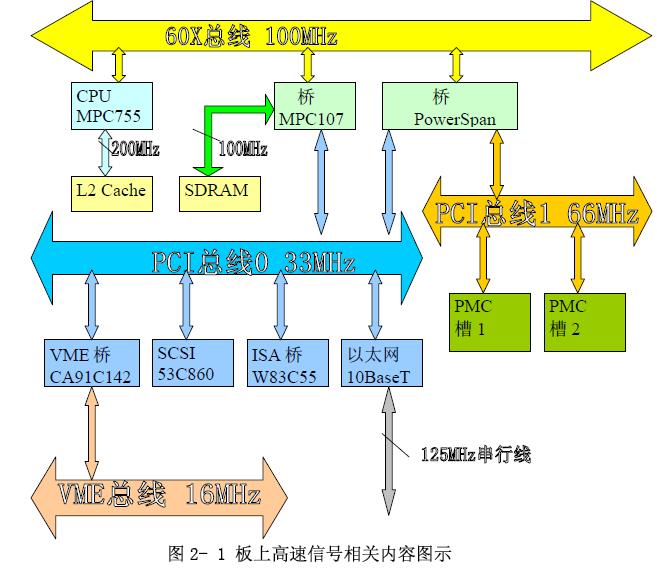

我們?cè)O(shè)計(jì)的是基于PowerPC的主板,主要由處理器MPC755、北橋MPC107、北橋PowerSpanII、VME橋CA91C142B等一些電路組成,上面的高速信號(hào)如圖2-1所示。

板上高速信號(hào)主要包括:時(shí)鐘信號(hào)、60X總線(xiàn)信號(hào)、L2Cache接口信號(hào)、Memory接口信號(hào)、PCI總線(xiàn)0信號(hào)、PCI總線(xiàn)1信號(hào)、VME總線(xiàn)信號(hào)。這些信號(hào)的布線(xiàn)需要特別注意。

由于高速信號(hào)較多,布線(xiàn)前后對(duì)信號(hào)進(jìn)行了仿真分析,仿真工具采用Mentor公司的Hyperlynx7.1仿真軟件,它可以進(jìn)行布線(xiàn)前仿真和布線(xiàn)后仿真。

2印制板信號(hào)完整性整體設(shè)計(jì)

2.1層疊結(jié)構(gòu)

在傳輸線(xiàn)(PCB走線(xiàn))中的磁力線(xiàn)是沿逆時(shí)針?lè)较虻模绻裄F返回路徑與對(duì)應(yīng)的源路徑平行并且與其靠近,在返回路徑中的磁力線(xiàn)(延逆時(shí)針?lè)较虻膱?chǎng)),相對(duì)于源路徑中的磁力線(xiàn)(順時(shí)針?lè)较虻膱?chǎng)),將是相反的方向。這樣順時(shí)針場(chǎng)和逆時(shí)針場(chǎng)可以抵消。如果源和返回路徑之間的磁力線(xiàn)被消除或減小,那么除了在走線(xiàn)附近極小的面積,輻射或傳導(dǎo)的RF電流就不存在了。多層印制板可以實(shí)現(xiàn)通量最小化,這是采用多層電路板的原因之一。信號(hào)層靠近參考層,信號(hào)返回路徑直接位于信號(hào)線(xiàn)的下方,回路面積最小,通量抵消最明顯。

為了實(shí)現(xiàn)通量最小化,必須實(shí)現(xiàn)PCB板上信號(hào)層和參考層交錯(cuò)排列,這樣,每個(gè)信號(hào)層都有相鄰的參考層。考慮到本板上的芯片數(shù)多,特別密集,而且電氣網(wǎng)絡(luò)也特別多,所以采用多少層的PCB要仔細(xì)安排,多了或少了都不好:如果層數(shù)太少,布線(xiàn)將變得很困難,甚至可能完不成布線(xiàn)。當(dāng)然在布線(xiàn)過(guò)程中如果感覺(jué)布線(xiàn)空間不夠,可以再增加層數(shù),但加層后要對(duì)已完成的布線(xiàn)做許多調(diào)整,重新安排一些走線(xiàn)規(guī)則,這將增加許多工作量。

如果層數(shù)太多,加工成本增加,板子厚度可能失控。目前4層板的板費(fèi)為0.5元/平方厘米左右,而六層板的板費(fèi)為1.5元/平方厘米左右。印制板層數(shù)每增加兩層,板費(fèi)要增加好幾倍。按VME64總線(xiàn)標(biāo)準(zhǔn),印制板厚度應(yīng)為1.6±0.2mm,即63±8mil,目前國(guó)內(nèi)的印制板設(shè)備,采用的板芯一般最薄的為5mil厚,銅層厚度有0.5盎司、1.0盎司、1.5盎司等規(guī)格,如果層數(shù)太多,印制板厚度無(wú)法滿(mǎn)足要求。

2.2阻抗考慮

PCI2.2規(guī)范要求PCB上的信號(hào)線(xiàn)在未焊接器件之前的特征阻抗為60Ω-100Ω,VME64規(guī)范要求PCB上的信號(hào)線(xiàn)在未焊接器件之前的特征阻抗為50Ω-60Ω。按目前的集成電路生產(chǎn)工藝,50Ω-100Ω的阻抗是比較合適的,不同的信號(hào)有一些差別。現(xiàn)在比較好的PCB加工設(shè)備,能加工線(xiàn)寬4mil、間距4mil的印制線(xiàn)。根據(jù)阻抗要求和目前PCB加工設(shè)備現(xiàn)狀,信號(hào)線(xiàn)基本采用5mil線(xiàn)寬和5mil間距,對(duì)有些信號(hào)線(xiàn)的阻抗,如果層間距和印制板基材介電常數(shù)調(diào)整無(wú)法滿(mǎn)足要求,可以采用4mil的信號(hào)線(xiàn)布線(xiàn)。

[page]

2.3傳輸速度

PCI2.2規(guī)范要求PCB上的信號(hào)線(xiàn)在無(wú)負(fù)載時(shí)的傳輸速度為150ps/inch-190ps/inch。PCB上的信號(hào)線(xiàn)在無(wú)負(fù)載情況下的傳輸速度只與介質(zhì)材料的介電常數(shù)相關(guān),所以選取介質(zhì)材料的介電常數(shù)時(shí)除了考慮它對(duì)印制線(xiàn)特征阻抗的影響外,還應(yīng)考慮它對(duì)印制線(xiàn)傳輸速度的影響。

2.4整板層疊及阻抗設(shè)計(jì)

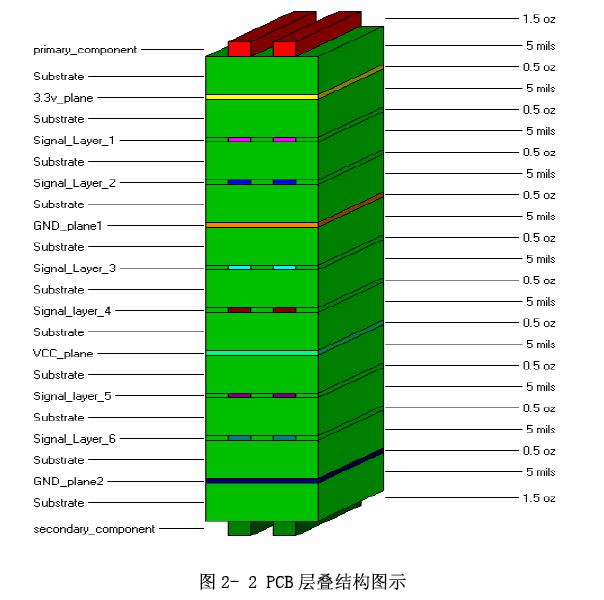

綜合以上三點(diǎn),最后采用12層印制板,其中8個(gè)信號(hào)層(包括元件層),兩個(gè)地層,一個(gè)3.3V電源層,一個(gè)混合電源層(包括5V、2V、兩個(gè)2.5V)。用HyperLynx軟件優(yōu)化出來(lái)的PCB層疊結(jié)構(gòu)如圖2-2所示,總厚度為65.7mil,即1.67mm,滿(mǎn)足VME64規(guī)范要求。

3時(shí)鐘信號(hào)阻抗匹配

時(shí)鐘信號(hào)是各設(shè)備工作的基礎(chǔ),所以時(shí)鐘信號(hào)的質(zhì)量尤為重要,在PCB設(shè)計(jì)時(shí)要慎重對(duì)待。

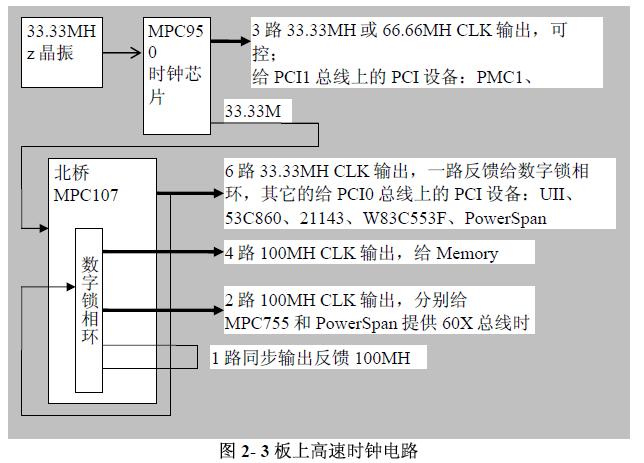

板上時(shí)鐘信號(hào)很多,主要高速時(shí)鐘信號(hào)如圖2-3所示。

時(shí)鐘芯片的輸出信號(hào)阻抗一般都比較小。芯片MPC950的輸出阻抗為7ohm,芯片AV9155的輸出阻抗為10ohm。本板上的時(shí)鐘信號(hào)都是點(diǎn)對(duì)點(diǎn)連接,所以采用串行端接進(jìn)行阻抗匹配電路設(shè)計(jì)。具體串連電阻的大小由HyperLynx仿真后決定。

[page]

4 L2Cache總線(xiàn)和60x總線(xiàn)信號(hào)完整性分析

本板的L2Cache總線(xiàn)工作頻率200Mhz,60x總線(xiàn)工作頻率100MHz,是板上工作頻率最高的部分。依據(jù)MPC755、MPC107、PowerSpan的芯片手冊(cè),阻抗在50ohm~70ohm之內(nèi)比較合適,按前面層疊結(jié)構(gòu)的設(shè)計(jì),5mil的信號(hào)線(xiàn)寬是可以保證阻抗要求的。

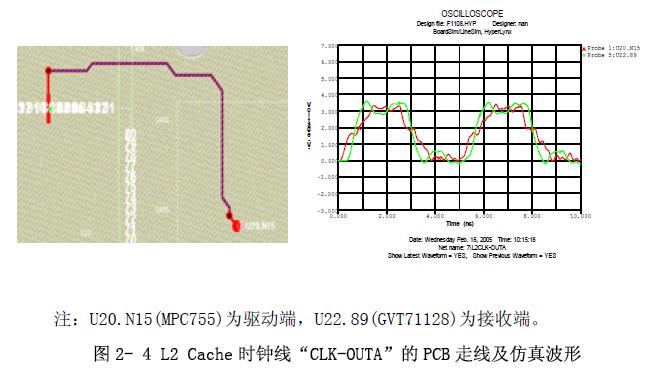

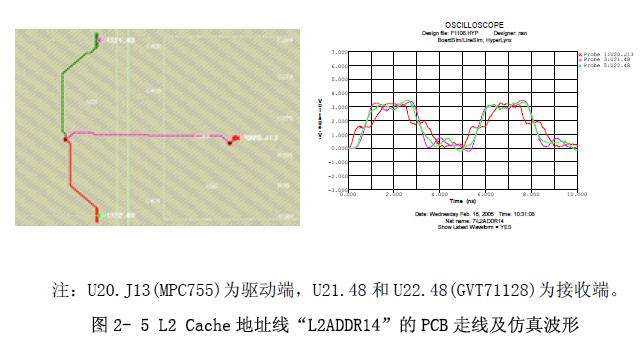

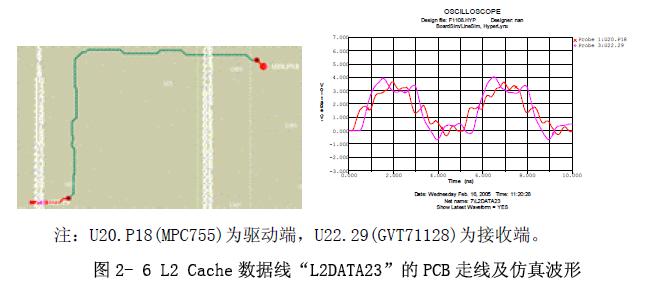

因?yàn)榘迳线@兩個(gè)總線(xiàn)的負(fù)載最多為2個(gè)負(fù)載,且這幾個(gè)芯片之間的距離很近,相關(guān)的PCB走線(xiàn)很短,所以信號(hào)時(shí)序關(guān)系一般能夠滿(mǎn)足要求(盡管其工作頻率很高)。下面給出L2Cache總線(xiàn)上典型時(shí)鐘線(xiàn)、地址線(xiàn)以及數(shù)據(jù)線(xiàn)的PCB走線(xiàn)圖以及在HyperLynx仿真軟件的BoardSim工具下的仿真波形。MPC755、MPC107、PowerSpan和GVT71128芯片的IBIS模型均來(lái)自于芯片廠商(Motorola、TUNDRA和GALVENTECH)。