- 采用2.5D IC堆疊技術

- 目前業界最大的容量

- 實現大容量系統集成,有效降低系統功耗

- 替代ASIC和ASSP

- 大規模系統集成應用

- ASIC的快速原型設計和模擬仿真

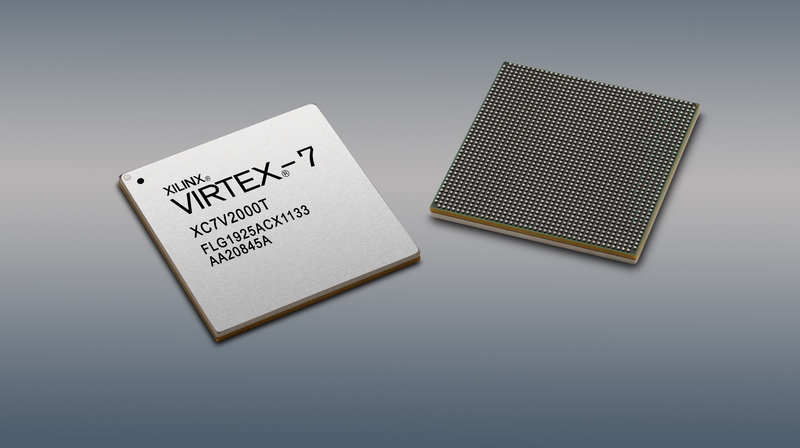

全球可編程平臺領導廠商Xilinx公司今天宣布,推出目前業界最大容量的FPAG產品Virtex-7 2000T。這款器件包含68億個晶體管的FPGA具有1,954,560個邏輯單元,容量相當于市場同類采用28nm制造FPGA容量的兩倍。這是Xilinx采用臺積電 (TSMC) 28nm HPL工藝推出的第三款 FPGA,而芯片容量提升主要歸功于Xilinx所采用的2.5D IC堆疊技術,這也是世界第一個采用堆疊硅片互聯(SSI) 技術制造的FPGA器件。

采用的SII技術的Virtex-7 2000T

Virtex-7 2000T中采用的SII技術,就是在無源硅中介層上并排連接著幾個有源硅切片,該切片再由穿過該中介層的金屬連接,與印制電路板上不同 IC 通過金屬互聯通信的方式類似。Virtex-7 2000T中包含了4個切片,因此其容量是市場同類最大28nm 器件的兩倍,而且比Xilins大型的Virtex-6 FPGA大2.5倍。

[page]

[page]

采用SSI技術制造出大容量的FPGA器件的意義在于,讓器件的發展步伐超過了摩爾定律的速度,因為按照摩爾定律,如果在單芯片器件中實現如此大的容量,必須等到下一個工藝節點才能實現。同時,盡管2000T由4個切片組成,但它仍保持著傳統 FPGA 的使用模式,設計人員可通過賽靈思工具流程和方法將該器件作為一款極大型 FPGA 進行編程。

SSI技術帶來的另一個特性,就是在實現大容量系統集成的同時有效降低了系統功耗。賽靈思Virtex-7 FPGA 產品線經理 Panch Chandrasekaran分析說,“市場上使用多個FPGA的最終產品非常多。有了Virtex-7 2000T,就能在單個FPGA上集成數個FPGA的功能。系統集成提高了性能,因為所有這些功能都集中在了一個芯片上,系統集成后,避免了開發板上不同 IC 間的 I/O 接口,從而降低了功耗。I/O 接口數量越多,功耗就越大,二者成正比關系。因此,設計性能越高、系統中 IC 數量越多,功耗也就越大。”

Virtex-7 2000T更大的應用空間

除具有 1,954,560 個邏輯單元外,Virtex-7 2000T還含有豐富的資源,包括305,400個CLB切片的可配置邏輯塊(CLB),21,550 Kb分布式RAM容量,2,160個DSP slice、46,512個BRAM、24個時鐘管理模塊、4 個 PCIe模塊、36個GTX收發器、24 個I/Obank和共 1,200 個用戶I/O。為設計者提供了更多的便利。

Xilinx認為,Virtex-7 2000T的主要目標應用包括三種:替代ASIC和ASSP,大規模系統集成應用、ASIC的快速原型設計和模擬仿真。

在 28nm 工藝技術節點,ASIC 或 ASSP 的NRE超過 5,000 萬美元,而 ASIC 修改則可能將成本再提升近一半。因此,除非面向最穩定的大批量市場應用,否則 ASIC 和 ASSP 的設計只會越來越少被采用。此外,競爭和縮短產品上市時間等這些市場壓力也為定制 ASIC 的開發帶來了挑戰。在此情況下,用一個 Virtex-7 2000T 器件來替代 ASIC,就能實現所需要的系統性能和功能。

在大規模系統集成設計上,核心的目標就是在提高系統性能的同時降低功耗,要想實現上述目標,一種途徑就是通過系統集成,減少板上不同 IC 間的 I/O 接口數量,從而降低功耗。此外還要注意,設計中使用的 IC 數量增多,在不同器件間進行設計分區的難度也會加大,這也會延長開發周期,提高測試成本,而采用 Virtex-7 2000T 器件則能避免上述問題。

就 ASIC 原型和模擬仿真而言,由于軟件開發在復雜系統開發周期中常常要占用大量的時間,通常要是等 ASIC 完成后才開始進行軟件開發,會耽誤整個系統的開發進度,有時甚至要耽誤長達 2 年的時間。有了 Virtex-7 2000T 原型或模擬仿真平臺,SoC 軟件開發就能大大提前,開發人員也不必再苦等 ASIC 的完成。

Xilinx公司全球副總裁湯立人先生認為,對于可編程邏輯器件技術來說,采用SSI技術的Virtex-7 2000T將是一個轉折點,新技術將使傳統的線性集成提升到非線性集成,將集成度提升到全新的水平。