中心議題:

- 邏輯分析儀介紹

- 邏輯分析儀的應用

- 配合調試工具單步調試程序

如今,嵌入式系統的功能越來越強,但設計和驗證問題也變得越來越復雜。善用邏輯分析儀,可以提高查找和解決問題的效率,尤其是最困擾嵌入式系統工程師的時序問題和一些硬件本身固有的問題。

邏輯分析儀介紹

邏輯分析儀(Logic Analyzer)是一種數字數據域測試的常用儀器,它可以把測試通道上的邏輯信號捕捉并存儲下來,供設計人員分析。與示波器相比,邏輯分析儀具有測量通道數多(一般有32個通道);觸發功能完善;分析功能強大等優點。

邏輯分析儀主要的技術指標有:

* 最高采樣頻率:最高采樣頻率越高,捕獲帶寬越高。

* 通道數:通道數越多,能同時捕獲的信號數也就越多。

* 存儲深度:存儲深度越大,能夠記錄的數據就越多。

* 輸入阻抗:輸入阻抗越高,對被測信號的影響越小。

* 觸發方式:觸發方式越多,使用起來越靈活。

其它技術指標還有:觸發門限電平范圍、是否有協議分析工具等等,這些都決定了邏輯分析儀的性能。

現在,邏輯分析儀的發展出現了兩種趨勢:傳統邏輯分析儀和虛擬邏輯分析儀。傳統邏輯分析儀功能強大,數據采集、分析和波形顯示融于一身,但是價格十分昂貴;虛擬邏輯分析儀是PC技術和測量技術結合的產物,觸發和記錄功能由虛擬邏輯分析儀硬件完成,波形顯示、輸入設置等功能由PC機去完成,因此不會對邏輯分析儀性能造成影響,同時節省了顯示和輸入方面的成本,在開發工程師熟悉的Windows操作系統下工作操作起來更加方便。與傳統邏輯分析儀相比虛擬邏輯分析儀具有質優價廉、方面使用等優點。

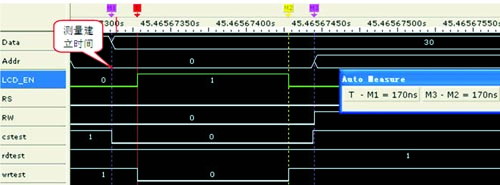

圖1 液晶時序圖

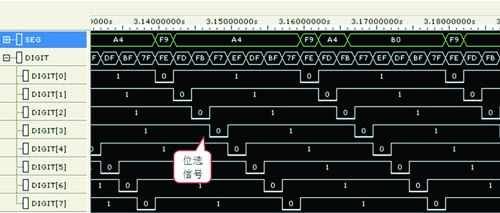

圖2 驅動數碼管的時序圖

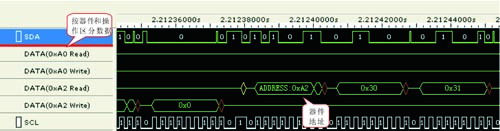

圖3 讀寫E2PROM存儲器時序圖

圖4 經I2C分析插件解碼后的時序圖[page]

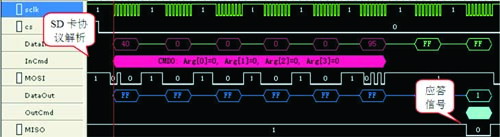

圖5 SD卡CMD0命令時序圖

應用

通常,嵌入式系統設計可以分為硬件部分和軟件部分,從硬件電路的調試到驅動程序的測試幾乎都需要邏輯分析儀的幫助。邏輯分析儀在嵌入式系統調試中的應用可以分為三個層次:

第一層:測試信號的時序和時間,這是邏輯分析儀最基本的應用;

第二層:利用邏輯分析協議分析的輔助功能,分析總線協議;

第三層:在線仿真器一起構成組合調試平臺,調試驅動程序。

捕獲毛刺

由于信號間延時不同,多路信號同時變化的瞬間往往會導致邏輯電路輸出中一些不正確的尖峰信號,這些尖峰信號稱為“毛刺”。另外,如果設備運行的環境比較惡劣,也會有高頻信號串入電路,造成毛刺。如果讓“毛刺”進入時鐘、清零和置位等對毛刺敏感的輸入端口,將會使電路產生不可預知的結果。

確定關鍵信號的建立時間和保持時間

建立時間(setup time)是指在觸發器的時鐘信號上升沿到來以前,數據穩定不變的時間,如果建立時間不夠,數據將不能在這個時鐘上升沿被打入觸發器;保持時間(hold time)是指在觸發器的時鐘信號上升沿到來以后,數據穩定不變的時間,如果保持時間不夠,數據同樣不能被打入觸發器。

液晶既是一個慢速設備也是一個對時序很敏感的設備。如果數據的建立時間不夠,很容易顯示亂碼。圖1是利用邏輯分析儀捕獲的液晶總線時序,并利用測量點來獲取建立時間和保持時間的信息。

驗證電路邏輯

電路設計好后,通常利用邏輯分析儀對輸入輸出信號進行采集分析,這樣可以比較可靠的驗證電路的邏輯功能。筆者為NiosII處理器設計了一個用于動態掃描8位數碼管的IP核,由邏輯分析儀捕獲的數據輸出如圖2所示。

分析總線協議

在確定關鍵信號路徑上無“毛刺”干擾,且建立時間和保持時間符合器件時序要求后,下一步就是分析器件間是否能正常傳輸數據,即協議是否正確。 MCU通過I2C總線對兩個外部E2PROM存儲器(器件地址分別是0xA0和0xA2)進行操作的時序圖如所示。

若工程師要根據邏輯電平的高低進行人工分析,顯然十分困難,更不要說區分哪些數據是發給E2PROM1的,哪些數據是發給E2PROM2的。這時,可以啟動邏輯分析儀的I2C分析插件。

常見的總線分析插件還有SPI總線、UART、1-WIRE、CF協議分析等。插件的種類會因廠商的不同而不同。

配合調試工具單步調試程序

嵌入式系統的開發人員通常使用在線仿真器(ICE)來完成軟件的調試,但隨著嵌入式系統復雜性的提高,單純的軟件調試已經很難適應需求。在線仿真器+邏輯分析儀已經構成一種新的組合調試平臺。借助邏輯分析儀可以發現許多隱匿很深的問題。例如,筆者在為NiosII處理器開發SD卡驅動的時候,遇到一個很奇怪的情況,SD卡命令已正確發送,邏輯分析儀也捕捉到了有效應答信號,如圖5所示,但是程序仍然返回應答信號等待超時錯誤。

單步調試程序發現,雖然邏輯分析儀捕捉到了有效應答信號,但是由SPI核讀入數據卻是0x80,即SD卡忙。最后,問題的原因是,Altera公司提供的SPI 核的CPOL=1,CPHA=0模式并不適合SD卡,將SPI核的工作模式設為CPOL=1,CPHA=1則驅動程序就可以正常工作了。

綜上所述,邏輯分析儀在嵌入式系統調試中的應用可以從基本數字電路的時序分析到器件間總線協議的分析,還以配合在線仿真器調試驅動軟件。借助在線仿真器+邏輯分析儀這種新的調試平臺,可以提高查找和解決問題的效率,增加產品的可靠性并能加快產品的上市速度。