- 時鐘抖動及測試方法的介紹和探討

- 時鐘抖動的分解

- 時鐘抖動測試注意事項

摘要

在高速互聯鏈路中,發送器的參考工作時鐘的抖動是影響整個系統性能的關鍵因素之一。本文對時鐘抖動的主要概念、測試方法及注意事項、測試難點進行分析和探討。

高速互聯鏈路介紹

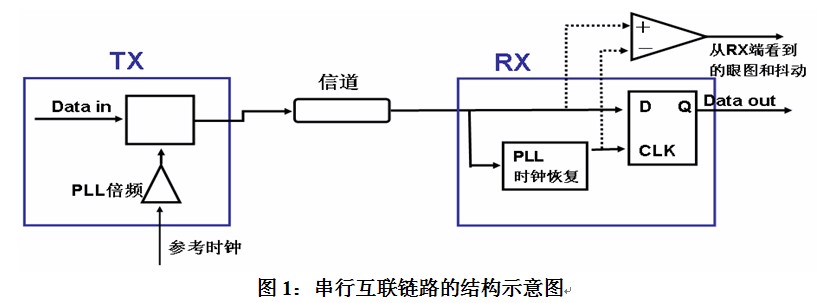

任何一個通信鏈路都包含三個部分:發送器(TX)、媒質(信道)、接收器(RX)。對于高速的串行互聯鏈路也包含這三個部分,如下圖1所示為一個典型的高速互聯鏈路的結構圖。其中發送器包括了:并行轉換串行、編碼(比如8b10b編碼)、發送信號優化(如預加重)、發送驅動等功能。接收器包括了:時鐘恢復、數據恢復、接收信號優化(如均衡)、串行轉化并行、解碼等功能。傳輸通道則由印刷電路板的走線、過孔、連接器、插卡的金手指、電纜、光纖等組成。

從整個鏈路的組成來看,發送器參考時鐘的抖動在串并轉換時就引入到整個鏈路中,影響著TX端發送出的數據的抖動,而接收器要從這些數據中恢復出時鐘來進行后續的處理。可以看出發送器參考時鐘的性能對整個鏈路的性能起到很關鍵的作用。本文從時鐘抖動的相關概念、測試實例、測試注意事項、測試難點幾方面對時鐘抖動測試進行分析和探討。

三種時鐘抖動的定義,峰峰值與有效值

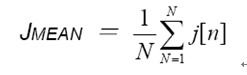

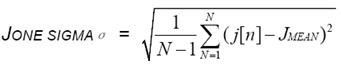

時鐘抖動通常分為時間間隔誤差(Time Interval Error,簡稱TIE),周期抖動(Period Jitter)和相鄰周期抖動(cycle to cycle jitter)三種抖動。

圖2:TIE Jitter抖動和TIE Jitter track

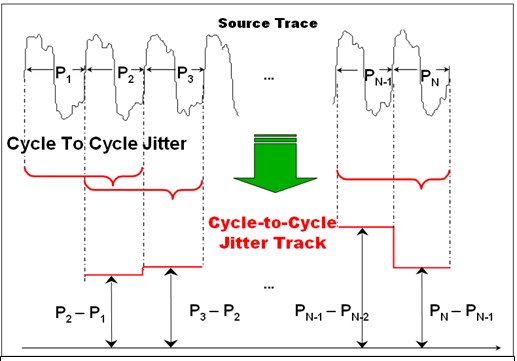

相鄰周期抖動(Cycle to cycle jitter)是時鐘相鄰周期的周期差值進行統計與測量的結果。如圖4所示,后一時鐘周期減去前一時鐘后作為統計的樣本,C1=P2-P1, C2=P3-P2, Cn-1 = Pn - Pn-1,把C1到Cn-1進行數理統計,同理,可以計算出Cycle to cycle jitter的峰峰值和RMS值。

圖3:Period Jitter抖動和Period Jitter track

圖4:Cycle to Cycle Jitter抖動和Jitter track

[page]

在圖2、圖3、圖4中的紅色曲線橫軸是時間,縱軸是對應周期的抖動數值,該曲線反映了抖動隨時間變化的趨勢,稱為抖動跟蹤(Jitter track);將每個周期的抖動值(比如TIE抖動的I1、I2…In)作統計直方圖,可以得到抖動直方圖(Jitter Histogram);將抖動跟蹤做快速傅立葉變換(FFT)計算可以得到抖動頻譜(Jitter Spectrum)。

抖動跟蹤是抖動在時域的表現形式,抖動頻譜是抖動在頻域的表現形式,抖動直方圖是抖動在統計域的表現形式。各種測試儀器和分析軟件對于抖動的測量和分析都是在這三個域中實現的。

如下圖5為某100MHz時鐘在時域、頻域、統計域分析其TIE抖動的示意圖。左上角的F2為某100MHz時鐘,P1是時鐘的TIE參數測量;右上角的F3是TIE抖動的直方圖,直方圖不是高斯分布,可見時鐘存在固有抖動。

圖5:時鐘抖動在時域、頻譜、統計域的分析

左下角的F4為TIE track(即TIE抖動隨時間變化的趨勢),從TIE Track中可以看到周期性的變化趨勢;右下角的F5是F4的FFT運算,即抖動的頻譜,頻譜的峰值頻率為515kHz,說明該時鐘的周期性抖動(PJ)的主要來源為515kHz,找到頻點后,可以查找電路板上主頻或諧波為該頻率的芯片和PCB走線,進一步調試與分析。時鐘抖動的分解

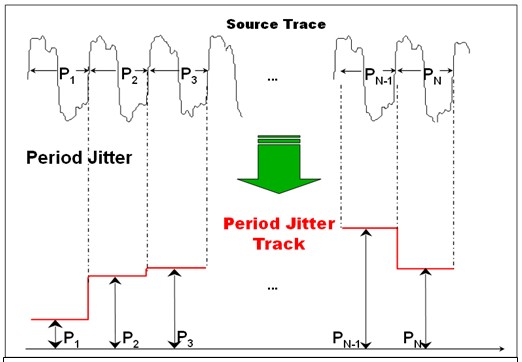

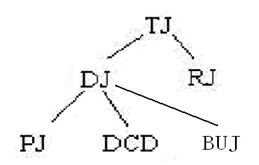

時鐘抖動的峰峰值和RMS值僅反映了抖動在統計上的數值,并沒有分析抖動的來源。對于時鐘抖動分解,業內通常把抖動分解為:總體抖動 (TJ)、確定性抖動(DJ)、隨機抖動(RJ)、周期性抖動(PJ)、占空比失真(DCD)等等。如下圖6所示為各種抖動的關系圖。

圖6:抖動的分解示意圖

RJ會隨著樣本數的增多不斷增大,其直方圖滿足高斯分布,通常用其統計后的1個Sigma或RMS值來表示,在抖動測試儀器中得到的RJ通常為RMS值。隨機抖動的來源為熱噪聲、Shot Noise和Flick Noise,與電子器件和半導體器件的電子和空穴特性有關,比如ECL工藝的PLL比TTL和CMOS工藝的PLL有更小的隨機抖動。

DJ是有邊界的、確定性的抖動,來源為:開關電源噪聲、串擾、電磁干擾等等,與電路的設計有關,可以通過優化設計來改善,比如選擇合適的電源濾波方案、合理的PCB布局和布線。

在抖動頻譜中,RJ是頻譜的基底部分,而DJ是抖動頻譜中的尖峰部分。很多測試儀器都是從抖動頻譜來分解抖動的。

時鐘抖動測試注意事項

在時鐘抖動測試中,有以下要點:

1, 選擇合適帶寬:為了準確測量到時鐘的邊沿,通常,示波器的帶寬在時鐘頻率的5倍以上,對于某些邊沿很快的時鐘,甚至需要儀器帶寬大于10倍時鐘主頻。

2, 選擇合適測試點:由于時鐘鏈路可能使用了各種端接策略或者星形拓撲結構,在發送端探測時鐘可能沒有太大的參考意義,通常是在時鐘鏈路的靠近接收端處探測和分析。

3, 保證地線盡量短:探頭的地線較長時,引入的寄生電感可能導致測量到的波形失真,較長的地線構成的信號環路也更容易受到電磁干擾。

4, 信號幅度盡量占滿整個屏幕:示波器的ADC只有8個比特的分辨率,必須讓信號幅度盡量占滿示波器的整個屏幕才可以保證足夠的測試精度。

5, 固定到合適的采樣率:使用合適的采樣率,保證在時鐘的邊沿采集到足夠的采樣點。

6, 抓取足夠的時鐘周期:對于有較低頻率的PJ的時鐘,需要捕獲足夠長的時間才能找到該時鐘的抖動來源。

時鐘抖動評估中的難點

在目前通信設備的時鐘的測試分析中,存在的問題為:芯片、設備、測試儀器廠商對時鐘抖動指標的含義定義不一致。比如有的芯片廠商直接給出抖動的pk-pk值,而沒有指明是那種抖動要求。芯片廠商給出的名稱與測試儀器廠商的名稱一致,但實際描述的含義卻不一致。

有的芯片廠商對時鐘抖動指標要求不嚴謹;有的芯片廠商給出的時鐘抖動的指標要求比較隨意,指標的給出沒有相應的根據。這些原因在于近十年來電子產品的運行速度和時鐘頻率不斷增加,而抖動的知識也在不斷完善與理論化,而某些芯片廠商的文檔對于抖動的定義不規范,給時鐘性能的評估帶來一定的困難,這些需要各自的積累來進行評估。

結語

高速鏈路是各電子設備以后重要的組成部分,其設計、性能分析和評估都是熱門的話題。本文僅對時鐘抖動的基本概念和測試進行相關的探討,而抖動各成分的分離技術、時鐘抖動在時域和頻域表現及他們的關系、抖動的來源、抖動的改善、抖動在不同應用場景下對系統的影響都是電路設計與測試工程師需要深入研究的內容。

參考文獻

1, 《jitter slides》----力科

2, 《Jitter, Noise, and Signal Integrity at High-Speed》---Mike Peng Li