- 無源探頭原理

- 改善SDRAM信號質量

- 串聯匹配是較好的SDRAM的時鐘端接策略

- 在原理圖設計中,需要加上串聯的電阻和并聯的電容

- 無源探頭在高頻時阻抗太小,不能準確的測量波形

- 需要使用高帶寬的有源探頭

前個周末接到了一個朋友的電話,詢問我如果內存有問題,需要測試哪些項目?對于這個很常見的問題,我習慣性的回答他先測量內存時鐘和讀寫時序看看,然后結束了通話。沒過一會,我那朋友又打過來,告訴我他遇到一個怪事,他用探頭點測內存時鐘時,系統的程序不卡了,可以順利啟動并運行。聽到這個描述,我頓時感興趣了,開始仔細詢問待測試的電路和測試儀器。

待測試的電路板的內存控制器為A公司的ARM架構的MCU,內存為Micron的SDRAM,內存時鐘頻率為100MHz,測試儀器為某200M帶寬示波器,探頭為示波器標配的無源探頭。在以往的探頭培訓中,我曾多次給客戶講探頭的重要性,在我的幻燈片中有以下幾句話:

在把探頭連接到電路上時,可能會發生下面三種情況:

1. 您可以把實際波形形狀傳送到示波器屏幕上。

2. 探頭可能會改變波形形狀,您會在示波器上觀察到不同形狀的信號。

3. 您可能會改變被測設備的運行(良好的設備可能會開始不能正確運行,或反之)

顯然,今天我這位朋友遇到的情況正好滿足第三種的最后三個字,即探頭使運行異常的設備變正常了。如果這樣的情況能經常發生,想必每位加班debug電路的工程師都可以不再苦惱,只需一個合適的探頭就可以找到問題原因并解決問題了。

從無源探頭的原理來看,如圖1所示為常見的無源探頭的簡化電路圖,通常示波器標配的無源探頭的直流輸入電阻為10兆歐(探頭的9兆歐與示波器前端1兆歐串聯),輸入電容為10pf左右,與9兆歐電阻并聯。當待測試信號的頻率較高時,容抗隨著頻率升高而減小,所以無源探頭整體的輸入阻抗變小,當頻率為100MHz時,輸入阻抗為159歐。

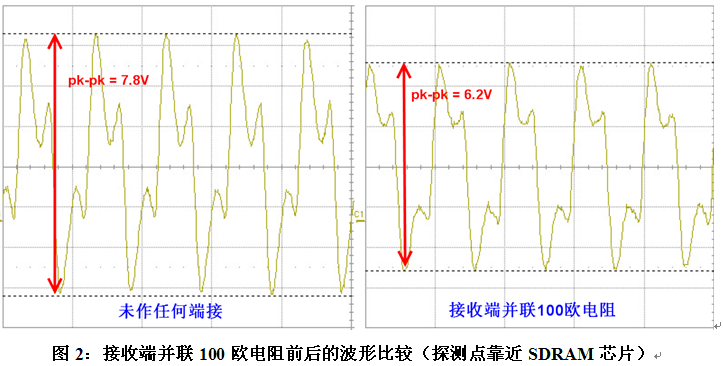

幾天后,我們在實驗室重新測試了該系統的時鐘,測試儀器為SDA816Zi(帶寬16G,采樣率40G),探頭為ZS1500(帶寬1.5GHz)。由于待測試信號頻率僅為100MHz,所以通常1G以上示波器和探頭足以滿足需求(注:對于某些上升時間很快的時鐘,比如PCIExpress的100MHz時鐘,1GHz的帶寬是不夠的,需要更高帶寬的示波器)。下圖2左圖為未作端接時在SDRAM芯片端測量時鐘波形,右圖為靠近SDRAM顆粒并聯100歐電阻后的波形,兩者相比,前者的過沖高達7.8V,電路板不能正常工作;而后者過沖較小,電路板可以正常工作。

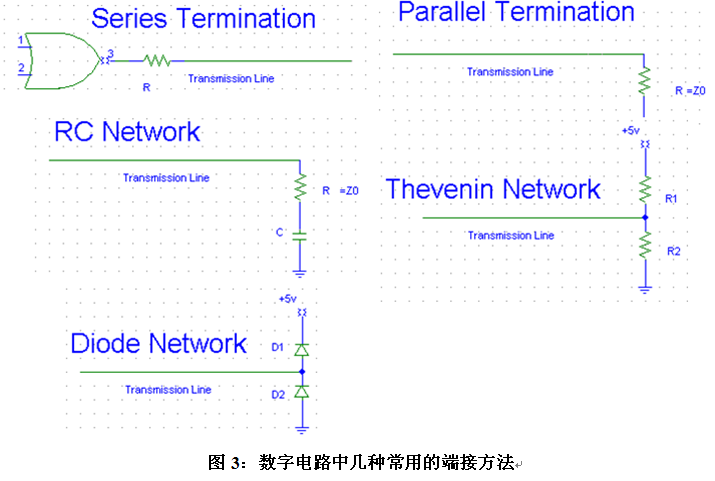

盡管并聯了100歐電阻后電路板能正常工作了,但是接收端測量到的峰峰值高達6.2V,對于SDRAM芯片3.3V的工作電壓來講還是比較大的,長期工作可能會導致內存芯片出問題,所以,我們還需改進端接策略。在信號完整性書籍中,通常有串聯匹配、并聯匹配、RC網絡、戴維南網絡等端接方法,如下圖3所示。相比并聯匹配,串聯匹配不用提供DC電流到地或者電源,不會對輸出的高低電平產生影響,能減小過沖和EMI,所以我們接著嘗試串聯匹配下的信號質量。

由于電路中ARM的MCU輸出的一路100MHz時鐘要驅動兩個SDRAM芯片,布線上MCU出來的時鐘剛出來就分成兩路后連向兩個SDRAM的時鐘引腳,所以我們采用了在兩路時鐘分支上同時串聯100歐電阻加并聯10pf電容的端接方法。在PCB上割線,焊上電阻和電容后測量的結果如下圖4所示,改進后的時鐘峰峰值為3.44V,波形無過沖,信號質量良好。電路板系統運行正常。

下圖5所示為只串聯100歐電阻時測量到的波形,信號有過沖,峰峰值為5.35V,偏大,對比圖4的端接方法,串聯電阻加上并聯電容是較好的解決方法。

總結:在這個案例中,我們得到的以下經驗:

1、 串聯匹配是較好的SDRAM的時鐘端接策略,在原理圖設計中,需要加上串聯的電阻和并聯的電容,如果MCU輸出的時鐘驅動能力弱,可以不使用并聯的電容或者換用較小的電阻。

2、 準確的測量內存時鐘需要足夠帶寬的示波器和探頭,無源探頭在高頻時阻抗太小,不能準確的測量波形,需要使用高帶寬的有源探頭。