【導讀】隨著市場需求推動存儲器技術向更高密度、更優性能、新材料、3D堆棧、高深寬比 (HAR) 刻蝕和極紫外 (EUV) 光刻發展,泛林集團正在探索未來三到五年生產可能面臨的挑戰,以經濟的成本為晶圓廠提供解決方案。

隨著市場需求推動存儲器技術向更高密度、更優性能、新材料、3D堆棧、高深寬比 (HAR) 刻蝕和極紫外 (EUV) 光刻發展,泛林集團正在探索未來三到五年生產可能面臨的挑戰,以經濟的成本為晶圓廠提供解決方案。

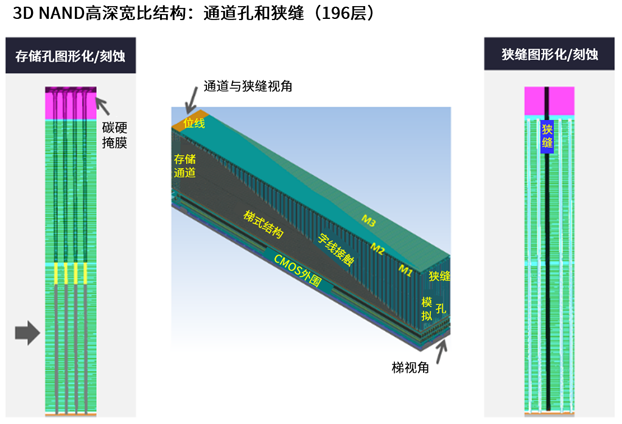

增加3D NAND閃存存儲容量的一種方法是堆棧加層,但堆棧高度的增加會帶來更大的挑戰。雖然這些挑戰中最明顯的是結構穩定性問題,但層數的增加意味著需要使用更深的通道來觸及每個字線、以及更窄的狹縫溝槽以隔離連接到位線的通道(圖1)。

圖1:隨著3D NAND堆棧超過128層,堆棧高度接近7微米,并將所需的通道孔和狹縫轉變為高深寬比 (HAR) 特征,刻蝕的挑戰越來越大。

高深寬比刻蝕的挑戰

在硬掩膜沉積和開口形成以便刻蝕垂直通道之前,沉積交替的氧化物和氮化物薄膜層就是3D NAND生產工藝的開始,高深寬比刻蝕挑戰也從這里開始。

隨著行業向128層及更多層數發展,堆棧深度接近7微米,硬掩膜的厚度約為2-3微米,通道孔的深寬比正在接近90到100。

在此之后,應對在大量層中形成狹縫的挑戰之前,會創建圖1所示的“梯式”結構。沉積一層硬掩膜,將開口圖形化并進行單步刻蝕以在所有的層形成狹縫。最后,必須去除氮化物層并創建鎢字線。

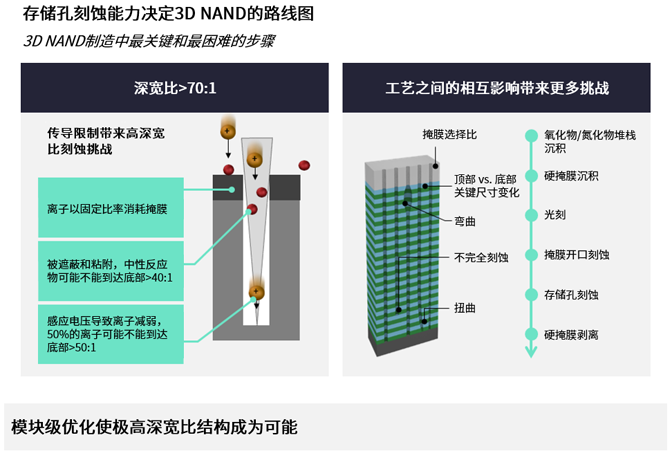

為了使高深寬比結構的反應離子刻蝕 (RIE) 起作用,離子和中性反應物之間必須有協同作用。然而由于多種機制的阻礙,處理高深寬比結構時,很容易失去這種協同作用。

圖2:離子和中性反應物被遮蔽,深寬比相關傳導以及離子角分布是導致關鍵尺寸變化、刻蝕不完全、彎曲和扭曲等缺陷的重要因素。

首先,高壓會導致等離子鞘層中的離子散射,并分散通常非等向性的離子能量或角分布。因此,離子會錯過孔或以更大的角度入射,撞到特征的頂部或側壁。這種離子“遮蔽”使離子-中性反應物通量比率偏離協同作用(圖2)。

如果將離子推下高深寬比特征,離子能量可能會增加,但這會增加掩膜消耗,反過來又需要更厚的掩膜或硬掩膜材料的創新。

除了這一挑戰,還有離子撞擊側壁并導致通道某些部位關鍵尺寸 (CD) 大于所需的問題。當這種“彎曲”(圖2)變得太大時,可能會導致兩個孔接在一起。

但還有一個更大的問題——沿孔“扭曲”,這是由于射頻等離子體系統中高階諧波變形的充電效應導致了離子角分布的輕微變化。

高深寬比刻蝕問題的解決方案

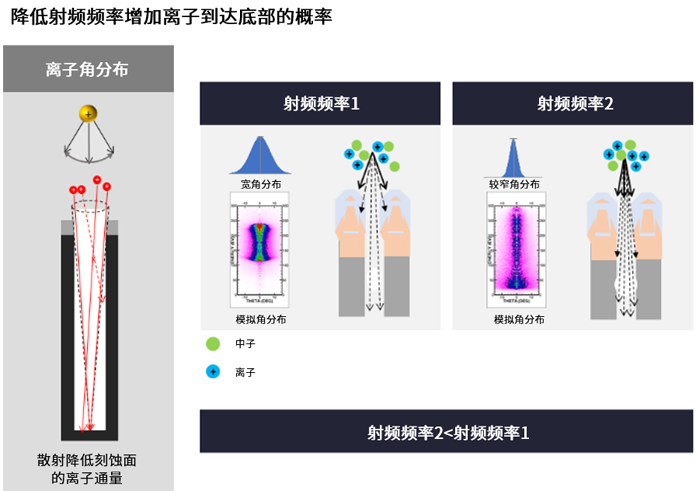

仔細觀察等離子體系統,尤其是射頻子系統,就會發現一個解決方案。事實證明,降低頻率,使得通過高壓鞘層加速的離子傳輸時間接近半周期,就能最大化給定射頻功率的離子能量峰值。頻率降低和離子能量峰值提升導致離子的角分布減小,使它們更有可能到達高深寬比特征的底部(圖3)。

圖3:降低等離子體頻率會減小離子的角分布,增加它們到達高深寬比特征底部的可能性。

因此,硬件設計專注向更低頻率、更高功率和更低占空比發展。

盡管改變了硬件設計,但在128層或更多層數的常用氧化物/氮化物 (ONON) 刻蝕6.9微米深的通道孔仍然非常困難。

因此,泛林正在測試一種不同的方法來實現所需的刻蝕深度,即先通過設定(例如5微米)刻蝕通道孔,然后在側壁上沉積保護性襯墊,以避免過度的橫向刻蝕。在隨后的步驟中,通道孔一直刻蝕到6.9微米。

添加襯墊以在不增加整個結構的關鍵尺寸的情況下進行額外的1微米刻蝕。雖然這個過程仍然需要諸多優化,但該測試展示了一條很有前途的、刻蝕更小更深孔的途徑。

圖形化面臨的挑戰和協同優化

邏輯和存儲的圖形化可能是芯片制造商削減成本和優化性能的重中之重。現在,這一切都關乎以最小的變化縮小到更小的結構。這種變化可以通過邊緣定位誤差 (EPE) 來衡量。

例如,對準孔面臨幾個變量的挑戰,例如線邊緣粗糙度、掃描儀套準精度誤差以及關鍵尺寸變化,包括由EUV曝光隨機誤差引起的局部關鍵尺寸變化。器件設計通常受限于變化的極值,而不是平均值。比如,管理這些變化以適應最壞的情況可能占用邏輯后端高達50%的區域,并大幅增加制造成本。

控制變化的一種方法是通過工藝間協同優化,這通常意味著在刻蝕期間補償光刻誤差。為了協同優化起作用,刻蝕設備必須具有合適的可調性,以更好地控制跨晶圓以及晶圓到晶圓的刻蝕行為。

因為晶圓總會遇到不同的等離子體條件和氣體分布,創造受控的溫度變化反過來可以使工藝具備可調性,并有助于補償腔室內和來自光刻機的變化。

控制溫度從而控制刻蝕速率的一種方法是在卡盤和晶圓上創建可調溫度區。十多年來,卡盤已從21世紀初期的單區設備演變為雙區設備,然后是徑向多區。最近,泛林的Hydra? Uniformity System中又演變到了非徑向多區。

簡化多重圖形化

主要用于DRAM和PCRAM、有時用于3D NAND的多重圖形化還面臨著關鍵尺寸變化的挑戰。圖形化方案增加了工藝步驟的數量,而這種增加意味著更多的變化來源。

在自對準四重圖形技術 (SAQP) 中,光刻、沉積和刻蝕的變化可能導致三種不同的關鍵尺寸。例如,在側墻刻蝕時,可能會挖入底層。這種變化導致“間距偏差”,這已成為多重圖形化的重大挑戰。

如果刻蝕后可以將側墻制成正方形,則可以克服這一挑戰,泛林已經通過創造性地使用新型金屬氧化物材料實現這一成果,無需深挖就可以將SAQP流程從八層簡化為五層。

EUV曝光隨機性的問題

EUV光刻預計很快就將成為邏輯和DRAM的主流,因此也需要仔細考慮由此工藝引起的變化。EUV光刻使用了高能量光子,并且該工藝容易受到隨機變化的影響。

對于孔,隨機行為會導致局部關鍵尺寸變化。在線和空間的情況下,線邊緣粗糙度 (LER) 和線寬粗糙度等缺陷帶來的影響是顯著的。

例如,隨機性限制通孔良率,并隨通孔關鍵尺寸縮放不良。在小通孔關鍵尺寸處,即使是250W的掃描儀功率也可能不夠,因此需要材料的創新以及后處理,以控制隨著功率增加帶來的EUV成本上升。

多年來,泛林在原子層刻蝕 (ALE) 方面的工作證明了該工藝能夠克服這一挑戰。原子層刻蝕包括表面改性繼而刻蝕的自限性步驟。當多次重復這一循環時,原子層刻蝕可以將特征的高頻粗糙度變得平整。

泛林及其合作伙伴在測試中測量了這種效應,EUV通孔局部關鍵尺寸均勻性 (LCDU) 因此提升了56%,從超過3納米變為1.3納米,對于某些芯片制造商來說可能還會降低到1納米。

局部關鍵尺寸均勻性的改善在上游有重要影響:由于泛林的刻蝕和沉積工藝可以減少隨機性引起的變化,因此EUV掃描儀可以使用更低的能量,這種光刻-刻蝕技術的協同優化可以將EUV成本降低兩倍。

建立實現路線圖的信心

現在,泛林已經為高深寬比結構以及原子層工藝開發了模塊級解決方案,以處理存儲器路線圖中的邊緣定位誤差。不過,為了沿著路線圖自信地前進,設備供應商、材料供應商和芯片制造商在工藝開發的早期階段必須共同努力,以經濟且高效的方式滿足存儲器路線圖的所有要求。

(來源:泛林半導體設備技術,作者:泛林集團 先進技術發展事業部公司副總裁潘陽博士、先進技術發展事業部 / CTO辦公室研究員 Samantha Tan 和全球產品事業部副總裁 Richard Wise)

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請電話或者郵箱editor@52solution.com聯系小編進行侵刪。

推薦閱讀: