【導讀】一般公司如果沒有人做這一塊,會要求設計師直接作出他電路的行為級模型,用來和數字組進行混合仿真。建模是一件不容易的工作,你如何證明你的建模能夠準確反映出你的模擬電路的特性?

仔細看過幾篇Kundert, K H的關于這方面的論文,我感覺這個還是很重要的。

一般公司如果沒有人做這一塊,會要求設計師直接作出他電路的行為級模型,用來和數字組進行混合仿真。

建模是一件不容易的工作,你如何證明你的建模能夠準確反映出你的模擬電路的特性?

Kundert, K H [1]提出的觀點為:

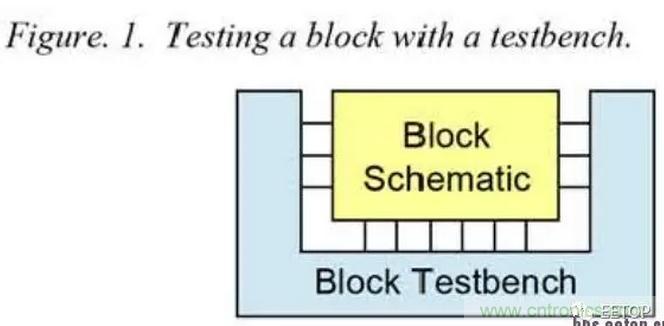

1. 用Verilog-AMS 寫出Testbench 去測試你的模擬電路,self-check。

如:驗證一個VGA,如果有64組控制字,Verilog-AMS 的Testbench要去完整驗證每一組控制字,做到self-check。

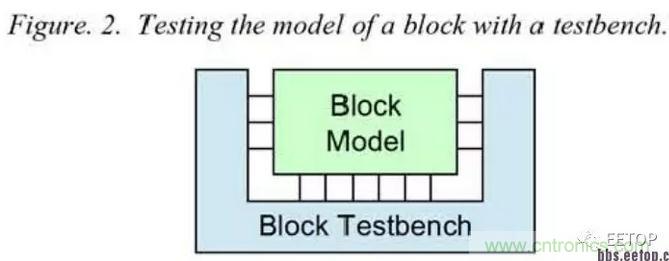

2. 寫出你模擬電路的行為級模型,做到pin-accurate(嘗試用行為級模型代表單個模擬電路版圖后仿結果),讓這個行為級模型能夠通過第 一步中你的testbench。

注:電路級模型,基本是沒有辦法和數字組做聯合仿真的,這個仿真時間可能是數以星期記。

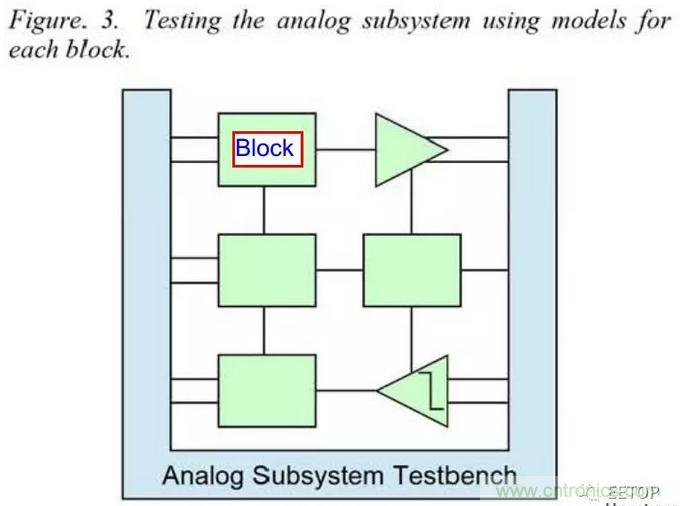

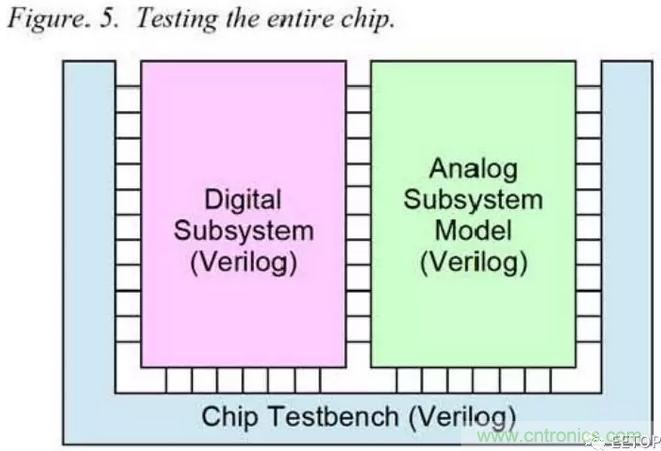

3. 將這個模型提供給數字組,進行混合仿真。或者提供給你其他部分電路用。

4. 如果仿真速度仍然很慢,嘗試用Verilog建立你模擬電路的行為級模型 (見[2], [3])。

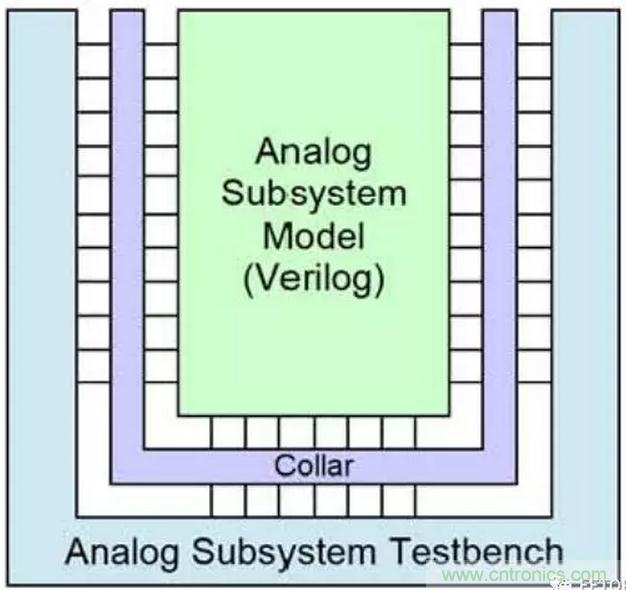

文獻[4] 給出了在Virtuoso (IC616)環境下,如何應用Verilog-AMS語言中的 wreal 數據類型 和 Verilog-2005,建立event-driven的模擬電路模型,極大提高仿真速度(1000倍以上)。

(注:Verilog-2005,內部支持real數據類型,但port不支持,需要通過 $realtobits 和 $bitstoreal 兩個函數來在不同module間傳遞real數據,而在Verilog-AMS和SystemVerilog-2012,可以直接傳遞real數據,前者引入了一中新的數據類型wreal,means wire real)

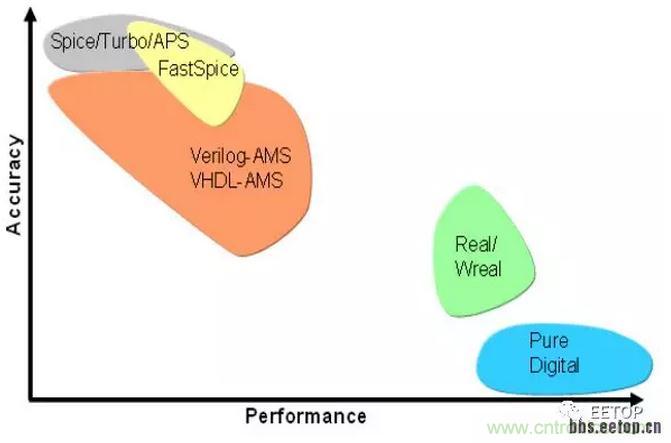

在Verilog-AMS中,我們可以用analog begin...end來建立模擬模型(如:Verilog-A中一樣),但這種建模方式仿真時,AMS Designer Simulator會調用模擬解法器來求解電路,而采用wreal 數據類型的event-driven建模方式,這樣 無論你的模擬電路和數字電路,AMS Designer Simulator都只會調用數字接法器,而大大提高功能級的驗證速度。各個建模方式的性能和仿真速度,如下圖:

event-driven的方式建模模擬電路模型,最早見于上世紀80年代末,當時還未有好的模擬電路建模語言,隨著Verilog-A和Verilog-AMS的出現,人們開始用模擬電路語言來建立模型,但又隨著數模混合電路規模越來越大,Verilog-A + Verilog的建模方式的仿真時間,越來越大,使得設計周期加大。于是,又開始重新研究event-Driven的建模方式。

目前,最新的成果[6],是利用一個時間離散點的值和這點的斜率,來近似這個點和這個點到下一個離散點之間的信息(Piece-wise Linear),而之前時間離散點之間的信息用上一個離散點的值表示(零階保持),(Piece-wise constant)。

因為SystemVerilog提供結構體數據變量,我們可以用值和它的斜率構成一個新的變量,用這個變量來描述模擬信號。更為精確的event-Driven的建模方式,需要在SystemVerilog中實現。

5. 全Verilog級的數模混合仿真,或者Verilog-AMS+Verilog的數模混合仿真

真實案例:

Min, H 給我們上課時,講過一個他們公司草創期的一個真實案例,就是開始時沒有模擬電路的行為級模型提供給數字組進行混仿,而又不可能拿電路級的去仿真,最后流片結果出錯,功能級不對,誤碼率偏高。然后,寫了模擬電路的行為級模型(Verilog-AMS)給數字組,在仿真階段就發現了這個誤碼率高的原因,給解決了。

我目前的科研項目中,就是一個比較大數模混合電路,直接開電路級混合仿真,需要好幾天,直接被我放棄,準備寫模型試試。

不知道大家怎么看,這個Analog 建模的方面。

參考 (點擊文末閱讀原文可下載參考資料)

[1] DCAS-2007, Kundert, K S, “Verification of Complex Analog Integrated Circuits”

[2] ECCTD-2013, Wegener, C (from Dialog Semiconductor), "Method of modeling analog circuits in Verilog for Mixed-Signal design Simulaitons"

[3] Forum on specification & Design Languages - 2014, Sabiro, S G (from Mentor Graphics), "Event-Driven (RN) Modeling for AMS Circuits"

[4] Cadence, Verilog-AMS Real Valued Modeling Guide - 2013

[5] TCAS-I-2014,Liao, S (from Stanford), "A Verilog Piecewise-Linear Analog Behavior Model for Mixed-Signal Validation"

[6] Cadence-2015, "Workshop for AMS Designer in Virtuoso"

網友互動摘錄:

kwankwaner:

我覺得行為模型在系統級仿真中既重要又方便,主要是驗證架構、算法、指標等等。至于做數模混仿我到覺得沒必要這么復雜,實際上數模相接的地方只有信號、電源和時鐘,這些完全都可以用一個描述清楚的源來代替。Q公司其實只要用Matlab建模就夠了,雙方把接口指標定義清楚就無需混仿。

作者答復:

Simulink建模確實最快最方便

- z-domain和s-domain可以放在一起仿真,采用ZOH連接

- 支持ModeSim - Simulink 和 Virtuoso - Simulink混合仿真

- 一直在推廣它內含的HDL-Coder,和HDL-Verifier。前者描述算法狀態機非常不方便,后者主要是用Simulink搭建仿真平臺去測試你的 Verilog。

MATLAB也在推它的混合信號仿真流程,以前做過一些調研,分享給大家

我問的一個QCOM的一個工程師,他說他們用Verilog-A挺多的,哈哈

但我感覺Verilog-AMS應該以后會用的越來越多。

angelaboy:

verillog-A and verilog-AMS都應該學習掌握吧!

作者答復:

Verilog-AMS 支持 Verilog-2005所有特性,同時支持模擬建模所有特性。 Verilog-A中不支持Verilog的語法。

Verilog-AMS最新標準是2014年6月發布的。

Verillog-A已經不更新了吧?

關于ADPLL行為級建模,采用Verilog-AMS,實際上仍然較慢。

25us仿真,Cadence AMS Designer,消耗我2.5小時;由于FMCW應用,我的仿真時間大約需要10ms左右。

采用全Verilog建模方式,1ms仿真時間,消耗2分鐘。

采用Simulink最快,但Simulink的建模層次最高,不利于挑出混合信號IC中的需要綜合部分的Verilog的錯誤。

因此,采用全Verilog方式,完成ADPLL建模,才是一個不錯的方案。

在一樓,分享了兩篇Verilog 對模擬電路建模的文章,希望大家喜歡。

以下省略更多論壇互動。。。

作者: JoyShockley(胡詣哲) 本文為作者為EETOP Analog IC設計板塊版主