【導讀】工藝技術不斷更新換代,推動了IC設計技術不斷提高。在設計密度、性能、節能燈特性方面都存在著諸多優勢和改進。但是同時新工藝還要求提升寄生參數提取精度,這就使得寄生電路提取面臨挑戰,新的寄生電路提取挑戰,看先進納米IC如何滿足新要求?

晶圓代工工藝技術的更新換代使IC設計密度、性能和節能特性得以不斷提高, 但也為設計人員帶來了更多挑戰。FinFET晶體管等創新的新工藝特性要求大幅度提高寄生參數提取精度,以通過仿真和分析來驗證實體設計的性能。本文將會介紹新的寄生電路提取挑戰,并探討工具技術是如何不斷發展以滿足新要求的。

提出新工具要求的原因

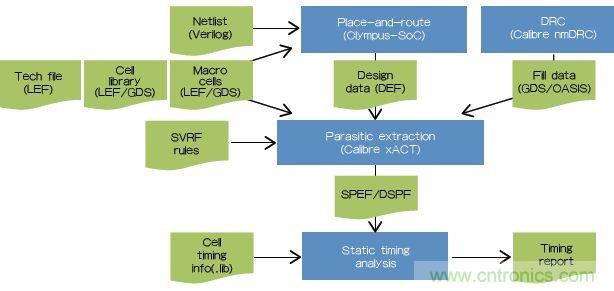

在IC采用了特定實體布局后,IC設計人員需要提取它的詳細電氣性能,以便進行靜態分析和仿真,確保IC能正常運行并滿足關鍵的性能要求。特別是針對16nm及以下的工藝,精確獲取FinFET器件中的寄生電阻和寄生電容,以及器件間的交互作用和與互連線相關的寄生電路至關重要。此外,不同的晶圓代工廠制作FinFET器件的方法存在差異。例如,有些晶圓代工廠在設計好的FinFET之間使用浮置器件,這樣一來,捕獲FinFET至浮置器件的耦合以及主要有源器件之間的耦合就非常重要。此外,FinFET中的寄生電阻也非常重要—隨著鰭形通道和源漏區變窄,源漏電阻增大,器件性能會有所降低。

雙重圖案工藝使問題變得更加嚴重,因為制造期間任何掩模失準都會增加或縮短多重圖案層上的特征圖案間距, 從而影響寄生電容的可預測性。因此,設計人員需要執行多重圖案角落(corner)的仿真來表征潛在的失準。在實踐中,這通常會涉及到超過10 個考慮工藝、溫度和雙重圖案(DP)角落。使用傳統工具時,全芯片抽取的時間通常為8至10小時(通宵);而采用雙重圖案工藝時,為提取全部所需的角落,處理較大的全芯片設計,經常需要花費更長的時間。有時,為節省時間,設計人員不得不限制定時分析,只運行少量精選的角落,這就增加了漏掉關鍵角落組合的風險。

另一大挑戰是先進工藝節點的大型設計所需金屬填充不斷增加,使寄生參數提取工具負荷劇增。提取工具必須讀取和處理數千兆字節的數據,才能準確建模填充圖案的密度和相鄰導線寄生電容。快速處理這些數據并制作簡化的填充模型,對維持工具產出及管理提取工具的內存使用而言非常重要。

處理節點到節點成指數式增加的器件數目和交互復雜性原本就很困難,而精度更高、模型更復雜、角落更多的要求使得挑戰更加艱巨,需要針對先進工藝節點完成大量的提取計算任務。即便如此,設計團隊還是希望周轉時間與之前節點處理時間一樣—確切來說,就是希望能夠通宵完成全芯片提取工作,這樣在第二天就可以繼續做設計工作。

新的工具方法

面對這些新的挑戰,EDA供應商不得不退而求其次,重新開始來創建全新的提取結構。Mentor Graphics公司希望可以提供具備以下功能的工具:

● 精度可媲美參考級提取工具(其缺陷是速度較慢)。

● 周轉時間與基于規則(rule-based)的工具保持一致(其缺陷是精度較低)

● 提取詳細的FinFET器件模型。

● 支持同步多角落提取。

● 將多重圖案技術融入提取流程中。

● 采用極快并高效的提取算法。

● 提供兼顧全芯片簽核和IP特征提取的協調一致的解決方案。

● 通過高級減縮技術提供快速的下游仿真。

● 支持大規模平行處理方法。

● 多個CPU內的SMP和網絡配置具備高度可擴展性。

要達到上述所有要求,需要結合多個創新方法來實現期望的功能。首先,要獲得最佳精度,就需要場求解器,其功能如名所示—以三個維度求解麥克斯韋偏微分方程。Mentor Graphics公司采用了一些既高效又高度平行化的創新型計算方法,使場求解器引擎的運行速度比傳統參考級場求解器快好幾個數量級。這將實現所需的阿托法拉級(AF)的精度,同時不會導致嚴重的性能損失。這是一項確定性技術(與Monte Carlo概率算法相比),能夠以接近零的平均誤差和低標準差來提供可重復的結果。

[page]

基于網絡的平行化和多CPU處理

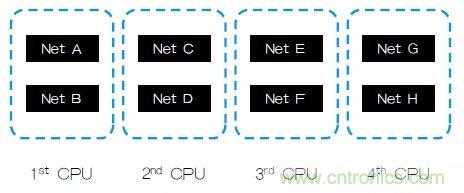

為獲得接近完美的可以大規模平行處理的線性縮放,Mentor Graphics引入了新的分解方法。與典型的片鋪(Tiling) 方法—將網絡劃分為眾多子網格來單獨處理不同,MentorGraphics所采用的方法可以保持網絡完整,并在專用CPU上處理各完整網絡。這種基于網絡的平行化方法消除了精度方面的限制和暈輪效應,提供了優于平鋪方法的可擴展性,特別是對于對稱多處理(SMP)機而言(圖1、圖2)。此外,基于網絡的平行化可以避免片鋪時由于CPU數量變化而引起的結果精度的差異。

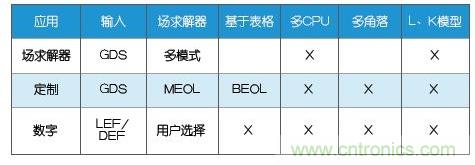

為進一步提高性能,新的架構針對精度要求較低的地方(例如上金屬層)采用了具備高度可擴展性的基于規則的技術。表1展示了Calibre xACT如何針對不同的幾何形狀和層來自動挑選合適的提取技術。

表1:CALIbRe xACT平臺針對特殊應用采取的最佳提取技術。

這些創新方法相結合能夠將提取性能提高三倍,或實現8個CPU每小時4~8百萬個網絡的處理量,以及達到最尖端的晶圓代工廠簽核要求的精度。通過新的Calibre xACT架構,提取有1百萬個臺的IP僅需15分鐘,而帶2千萬網絡的全芯片提取也能在一夜之間完成。對于更大型的設計,可以通過增加額外的CPU來處理。

針對需要很多提取角落的設計,這款新平臺執行同步多角落提取,各個角落的運行時間減少了15%~20%,而精度絲毫不受影響。由于該平臺使用確定性技術,單一角落和多角落運行始終能夠提供同樣的結果,Monte Carlo方法則無法做到如此。

[page]

選擇性網絡處理和網表簡化

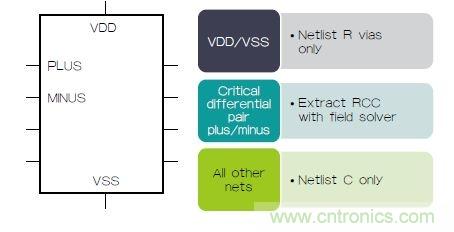

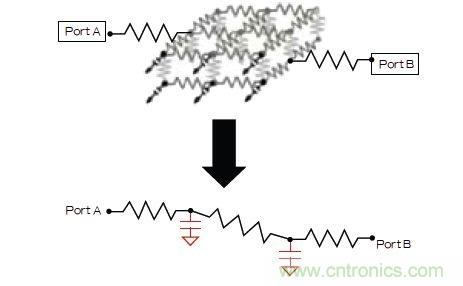

加速周轉時間并同時減少管理數據量的另一個方法是選擇性網絡處理技術。通過該技術,設計人員可以為各個網絡選擇特定的寄生模型,從而定制針對仿真而生成的數據量(圖3)。設計人員可以按各個網絡逐個選擇分散RCC(帶耦合電容)、RC(不帶耦合電容)、C或R,或依各層來控制提取。例如,為降低仿真時間,同時顧及大功率網絡和地線網絡的寄生效應,設計人員可以提取僅包含過孔電阻而排除金屬層電阻的VDD和VSS網絡。這個功能特別有用, 因為過孔對電源/地線網絡形成的電阻最大。該功能可以加快仿真速度,同時維持所需的設計裕量。

另一個節省時間的方法是從單個寄生參數提取數據庫(或提取運行)生成多個網表。這個方法可用于生成多種網表格式和具備多寄生模式的網表,其可以根據各個網絡進行控制。通過這種方法,設計人員無需在每次生成不同網絡時運行提取,從而節省了時間;此外,還可以針對單個提取運行進行多個布局后分析。例如,設計人員可以在設計的所有網絡上執行單個RCC提取運行;然后以RCC網絡模型生成所有信號網絡的SPICE網表,以進行時序分析;最后生成一個DSPF格式的僅包含電阻的網表,以用于電遷移分析。

仿真器性能在很大程度上取決于網表的大小,而寄生元件可能使網表尺寸成數量級增加。精度越高意味著寄生參數越多,但電路就會更加復雜,分析時間也會更長。這就是靈活的網表簡化技術至關重要的原因—它可以盡可能地減少用于布線后仿真的寄生電路數據量,僅生成所需的寄生電路數據(圖4)。這樣不僅提高了仿真性能,還減少了分析時間和收斂性問題。

結語

數字、定制、模擬或RF設計團隊在處理任何節點,特別是16nm或更小的節點時,需要有比以往所有工具速度更快、精度更高、靈活性更強的提取工具。為應對挑戰,EDA供應商需采用基于更高級架構和算法的新提取工具來獲得所需功能。

相關閱讀:

DC-DC轉換器中PCB布線寄生電感對于效率的影響

電容傳感器寄生電容干擾的產生原因及消除方法

高度挑戰!明導關于鰭式場效晶體管寄生提取的復雜性報告