【導讀】為適應VLSI集成密度和工作速度的不斷提高,新穎的集成電路NSD保護電路構思不斷出現。本文將對ESD失效模式和失效機理進行了介紹,著重從工藝、器件和電路3個層次論述ESD保護模塊的設計思路。

靜電在芯片的制造、封裝、測試和使用過程中無處不在,積累的靜電荷以幾安培或幾十安培的電流在納秒到微秒的時間里釋放,瞬間功率高達幾百千瓦,放電能量可達毫焦耳,對芯片的摧毀強度極大。所以芯片設計中靜電保護模塊的設計直接關系到芯片的功能穩定性,極為重要。隨著工藝的發展,器件特征尺寸逐漸變小,柵氧也成比例縮小。

二氧化硅的介電強度近似為8×106V/cm,因此厚度為10 nm的柵氧擊穿電壓約為8 V左右,盡管該擊穿電壓比3.3 V的電源電壓要高一倍多,但是各種因素造成的靜電,一般其峰值電壓遠超過8 V;而且隨著多晶硅金屬化(Polyside)、擴散區金屬化(Silicide)、多晶硅與擴散區均金屬化(Salicid)等新工藝的使用,器件的寄生電阻減小,ESD保護能力大大減弱。

為適應VLSI集成密度和工作速度的不斷提高,新穎的集成電路NSD保護電路構思不斷出現。本文將對ESD失效模式和失效機理進行了介紹,著重從工藝、器件和電路3個層次論述ESD保護模塊的設計思路。

1 ESD的失效模式

因ESD產生的原因及其對集成電路放電的方式不同,表征ESD現象通常有4種模型:人體模型HBM(Hu-man-body Model)、機器模型MM(Machine Model)和帶電器件模型CDM(charged-Device Model)和電場感應模型FIM(Field-Induced Model)。HBM放電過程會在幾百納秒內產生數安培的瞬間放電電流;MM放電的過程更短,在幾納秒到幾十納秒之內會有數安培的瞬間放電電流產生。 CDM放電過程更短,對芯片的危害最嚴重,在幾納秒的時問內電流達到十幾安培。

ESD引起的失效原因主要有2種:熱失效和電失效。局部電流集中而產生的大量的熱,使器件局部金屬互連線熔化或芯片出現熱斑,從而引起二次擊穿,稱為熱失效,加在柵氧化物上的電壓形成的電場強度大于其介電強度,導致介質擊穿或表面擊穿,稱為電失效。ESD引起的失效有3種失效模式,他們分別是:

硬失效:物質損傷或毀壞;

軟失效:邏輯功能的臨時改變;

潛在失效:時間依賴性失效。

2 MOS集成電路中常用的提高ESD能力的手段

2.1 從制程上改進

目前從制程上改進ESD保護能力有2種方法:增加ESD注入工序和增加金屬硅化物阻擋層掩模版。這兩道工序提高了器件承受ESD的能力,但同時也增加了工藝成本。

2.1.1 ESD注入工序(ESD Implantation)

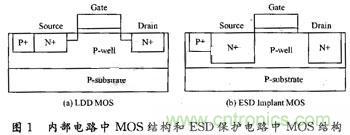

在亞微米工藝中,引進了漏端輕摻雜工序(Low Do-ping Drain)見圖1(a),這步工序在源端和漏端與柵極重疊的地方生成一個輕摻雜濃度的淺結,可以降低漏端在溝道中的電場強度分布,從而克服因熱載子效應 (Hot CarrierEffect)所造成的器件在使用長時間后Vth漂移的問題。該淺結一般只有0.2 m左右深,形成曲率半徑比較小的尖端,靜電通過時,會在該尖端先放電引起結的擊穿,導致熱失效。采用LDD結構的MOS器件作輸出級,很容易被靜電擊穿,HMB測試擊穿電壓常低于1 000 V。

在輸入/輸出端口處的MOS器件上增加ESD注入層見圖1(b),ESD Implantion可以制備深結的傳統MOS器件,從而提高亞微米工藝下器件的ESD保護能力;在內部電路仍然使用有LDD結構的MOS器件。這樣在提高器件性能的同時又增加了ESD的保護能力。例如在相同chan-nel width(W=300μm)情形下,LDD結構的 NMOS器件,其ESD防護能力只有約1 000 V(HBM);但ESD-Implant的NMOS元件,其ESD防護能力可提升到4 000 V。

圖1:內部電路中MOS結構和ESD保護電路中MOS結構

2.1.2 金屬硅化物阻擋層(Silicide Blocking或Sali-cide Blocking)

Salicide Blocking工藝增加一張掩模版定義SalicideBlocking區域,然后去除該區域的金屬硅化物,使源、漏和柵的方塊電阻值恢復到原來的值,靜電放電時經過大電阻時產生大的壓降,同時電流減小,達到提高ESD的保護能力。增加Salicide Blocking工序,可以極大程度的提升CMOS IC輸出級的ESD保護能力,但是Salicide Blocking工序也增加了工藝的復雜度,而且在去除金屬硅化物的同時,會對工藝線造成污染。

2.2 從器件上改進

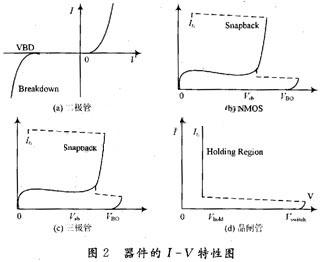

器件在不同偏壓下的特性和占用的布局面積是考核ESD器件的指標。圖2是各種用作ESD保護器件的I-V特性圖。圖2(a)二極管正向工作電壓約在0.8~1.2 V左右,但是反向工作電壓約在-13~-15 V左右。因此,當相同大小的ESD放電電流流經該二極管時,在反向靜電壓下產生的熱量遠大于正向靜電壓情形下產生的熱量,即二極管能承受的正向ESD電壓將遠大于反向ESD電壓。

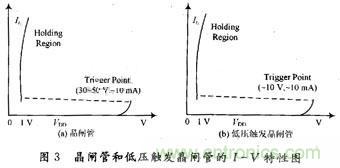

圖2(b)MOS和圖2(c)三極管的ESD承受能力與二次崩潰點電流It2有關。當ESD放電電流大于該器件的It2,該器件便會造成不可回復性的損傷,且二者的箝制電壓一般較大,導致功率較高。圖2(d)晶閘管(SCR)在正偏與反偏時工作電壓都只有1 V左右。對比4種器件可看出晶閘管的箝制電壓更低,所以功耗最小,晶閘管通過相同的電流時占用的面積也小,綜上晶閘管是最理想的ESD保護器件。

圖2:器件的I-V特性圖

圖3:晶閘管和低壓觸發晶閘管的I-V特性圖

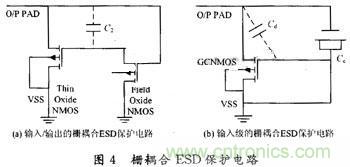

針對ESD放電的瞬間電壓快速變化,借助電容耦合(coupling)作用使ESD防護電路達到更有效率的保護能力。

在亞微米工藝下,輸入/輸出PAD處的ESD保護用的MOS一般W/L的值較大,在布局上經常畫成叉指結構。但是,在ESD放電發生時,各個叉指不一定會同時導通,若只有2~3支叉指先導通,ESD電流便集中流向這2~3支叉指,該器件的ESD防護能力等效于只有2~3支叉指的防護能力。為克服大尺寸晶體管不均勻導通的情況,可以利用電容耦合作用來使大尺寸晶體管的每一叉指都能均勻地導通。

圖4(a)利用電容耦合作用使大尺寸晶體管均勻導通,NMOS的雜散Cgd電容做耦合器件,通過場氧NMOS加強了耦合電容的效用,當正的ESD電壓突然出現在PAD上時,由于電容耦合作用NMOS柵極電壓跟著上升,故大尺寸NMOS均勻導通而進入驟回崩潰區(snapback region),ESD放電能量便可均勻分散到每一叉指來承受,真正發揮大尺寸晶體管器件應有的ESD防護水準。

圖4(b)是電容耦合技術應用于輸入級ESD防護電路上的一種安排,GCNMOS(Gate-Couple NMOS)是ESD電流旁通用的器件,尺寸較大。

圖4:柵耦合ESD保護電路

3 結 語

MOS集成電路ESD保護電路基于工藝級別、器件級別和電流級別的改進,已有大量優秀的ESD保護電路出現,ESD保護電路強度已超過2 000 V(采用HBM模型試驗)。幾種方法結合制造的ESD保護電路,如采用柵耦合PTLSCR/NTLSCR ESD保護電路,可有效的對深亞微米CMOS IC薄柵氧化層保護,而且占用的版圖面積只占傳統ESD保護電路的1/2左右。

相關閱讀:

ESD問題及抑制解決方案

小尺寸、大用途,超低電容ESD保護方案

硅基器件在平板電腦各模塊ESD中的應用