【導讀】預偏置晶體管是在制造過程中集成了偏置電阻的晶體管。這種設計具有成本效益,集成的元件節省了印刷電路板(pcb)的成本,并減少了物料清單(BOM)中的項目數量。一個典型的產品是 Diodes 的 DDTD113ZC-7-F NPN 晶體管,采用 SOT - 23 - 3 封裝,如圖 1 所示。這種預偏置晶體管包括一個 1 千歐的串聯限流電阻,以及一個與基極 - 發射極結并聯的 10 千歐關斷電阻。

本文總結了預偏置晶體管的定義、作用、電路分析及設計要點,強調其在減小PCB尺寸、降低元件數量方面的優勢,并提醒合理選擇以匹配微控制器與負載。

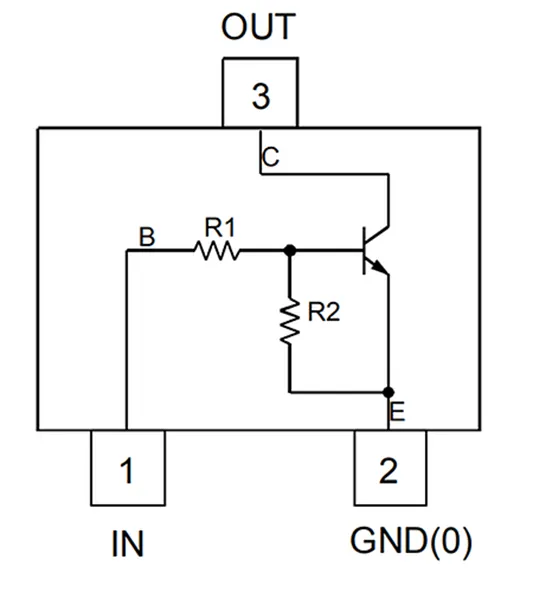

預偏置晶體管是在制造過程中集成了偏置電阻的晶體管。這種設計具有成本效益,集成的元件節省了印刷電路板(pcb)的成本,并減少了物料清單(BOM)中的項目數量。一個典型的產品是 Diodes 的 DDTD113ZC-7-F NPN 晶體管,采用 SOT - 23 - 3 封裝,如圖 1 所示。這種預偏置晶體管包括一個 1 千歐的串聯限流電阻,以及一個與基極 - 發射極結并聯的 10 千歐關斷電阻。

預偏置晶體管在電路中如何使用?

預偏置晶體管設計用于與微控制器等數字邏輯直接連接,從而無需額外的輔助電阻。這樣可以實現緊湊的 PCB設計,并減少元件數量,因為三個傳統元件被集成到了單個封裝中。

預偏置晶體管中每個電阻的作用是什么?

串聯限流電阻 :與 LED電路中的串聯電阻類似,該串聯電阻用于限制基極電流。 關斷(分流)電阻 :與晶體管基極 - 發射極結并聯的這個電阻有助于晶體管關斷。當輸入串聯電阻斷開時,例如微控制器 I/O在啟動時設置為高阻抗或處于超低功耗(ULP)模式時,它提供一個泄漏路徑,使基極保持在零伏。這個關斷電阻還有助于降低ICE(集電極 - 發射極)間的泄漏電流。

市場上有多種預偏置的 NPN 和 PNP 晶體管可供選擇。設計人員可以選擇具有最合適的串聯電阻和關斷電阻的產品,以匹配其應用需求。

數字(開關)電路中強制 β 操作的必備晶體管理論

晶體管的特性之一是其直流電流增益(β),它被定義為集電極電流與基極電流之比。對于在其線性區域工作的晶體管,這是模擬設計中的一個重要指標。

在數字(開關)設計中應避免線性操作。相反,我們將重點關注強制 β。通過這種設計技術,我們有意使晶體管過驅動,以確保其完全飽和,從而特意避開線性區域。作為初步估計,我們假設強制 β 為 10,但要注意,強制 β 明顯低于線性 β。

預偏置晶體管電路的電路分析

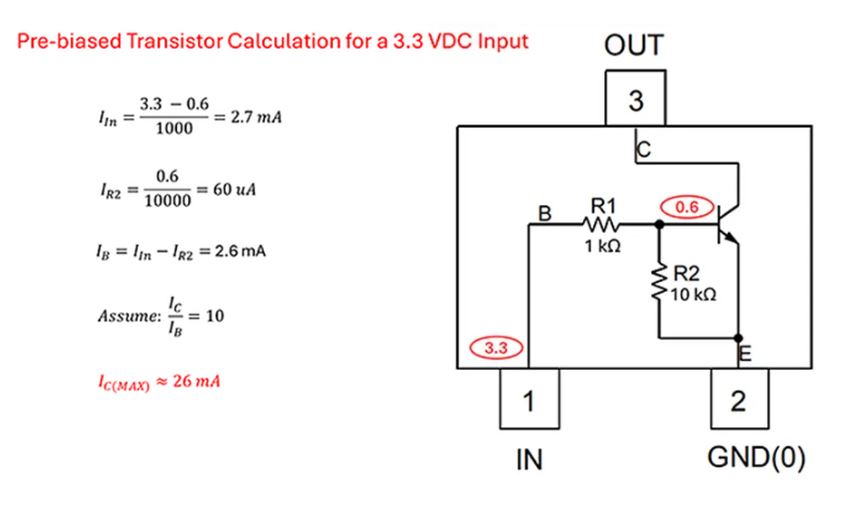

圖 2 展示了Diodes DDTD113ZC - 7 - F 的電路分析。該晶體管的 R1 值為 1 千歐,R2 值為 10 千歐,并且具有高增益。

R1 串聯電阻將輸入電流限制在 2.7 毫安。這是一個相對較低的驅動電平,大多數微控制器都能輕松提供。然而,正如在下一個技術小貼士中所探討的,這個值可能仍然過高。 關斷電阻消耗一小部分輸入電流。根據所選預偏置晶體管的 R1 與 R2的比率,這對電路計算可能重要,也可能不重要。 基極電流計算為輸入電流減去關斷電阻電流。 假設處于強制 β 條件下,最大集電極電流計算為基極電流的十倍。請注意,這是一個保守估計,用于確保晶體管進入飽和狀態。您可以通過測試設計中的極端情況來改善這種情況。

圖 2:由 3.3 伏直流邏輯驅動的 Diodes DDTD113ZC - 7 - F 的電路分析

技術小貼士:

典型的微控制器有兩個電流規格,包括每個引腳的規格和所有引腳電流的總和。例如,瑞薩電子 Renesas 的 R7FA4M1AB3CFM#AA0,用于最新的 Arduino UNO R4 開發板。大多數端口能夠吸收和輸出 4 毫安電流,少數引腳能夠承受 20 毫安電流,但所有輸出引腳的總電流限制為 60 毫安。因此,需要進行仔細的電路分析,以確保不超出產品的限制。

請注意,這里展示的 Diodes 的 DDTD113ZC-7-F 預偏置晶體管因其 R1 電阻值較低而被選用。對于低電流微控制器,具有較高輸入電阻的晶體管可能是更好的匹配。

務必逐個案例(逐個負載)進行評估。

預偏置晶體管的速度有多快?

晶體管的開啟和關斷速度由負載特性、米勒電容和飽和深度等因素決定。以下是一些與本工程簡述直接相關的設計考慮因素:

深度飽和的晶體管關斷速度會很慢。根據定義,強制 β 偏置會使晶體管深度飽和,以避開線性區域。這是一個重要的考慮因素,因為在載流子從其硅結構中清除之前,晶體管不會關斷。 基極電流取決于微控制器的 I/O 電壓以及預偏置晶體管的 R1 / R2 比率。飽和深度也取決于負載。例如,當負載接近 26 毫安的限制時,所示電路的速度比輕載 5 毫安時更快。換句話說,要仔細選擇預偏置晶體管以匹配負載,避免過度飽和。 與微控制器的直接連接排除了施加負脈沖以提高關斷速度的可能性。此外,由于沒有暴露的基極連接,無法實現諸如貝克鉗位等加速電路。

綜合來看,這些設計限制表明預偏置晶體管以中等速度運行。然而,有許多不同的負載和電平轉換應用可以從預偏置晶體管中受益。在所有情況下,設計人員都應選擇最合適的預偏置晶體管,以使微控制器與負載實現最佳匹配。

技術小貼士:

請記住,傳統上匹配過程是通過選擇合適的電阻來完成的。現在,設計人員必須選擇具有適合手頭任務的內部電阻的預偏置晶體管。例如,R1 為 4.7 千歐甚至 10 千歐的晶體管可能更適合您的設計。

最后

預偏置晶體管是一種方便的方法,可以減小 PCB 尺寸并減少設計中使用的元件總數。務必通過選擇具有適當內部電阻的預偏置晶體管,使微控制器與負載相匹配。

本文轉載自:DigiKey電子技術臺

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理。

推薦閱讀:

利用定制DSP指令增強RISC-V RVV,推動嵌入式應用發展

第十三屆中國電子信息博覽會觀眾登記全面開啟,精彩盛宴,等您來赴!