【導讀】在快速 VLSI 電路中,晶體管每秒開關數百萬次。在開關過程中,被稱為“熱載流子”的高能載流子(電子或空穴)很容易注入并捕獲在柵極氧化物中。這種熱載流子注入會導致柵極氧化物中出現雜質,從而改變器件的 I-V 特性。

在非常小的晶體管中,柵極氧化物可能只有幾個原子厚。雖然這使得器件小型化,但也會由于電流隧道效應而導致泄漏。

此外,隨著設備老化,這種不理想的情況會變得更糟,因為氧化物會磨損。結果,閾值電壓發生變化,這進一步增加了柵極泄漏。這種效應更顯著的影響是晶體管失配或高漏電流會導致電路故障。

氧化物磨損的三個主要原因是:

熱載流子

負偏壓溫度不穩定性 (NBTI)

隨時間變化的介電擊穿 (TDDB)

熱載體

在快速 VLSI 電路中,晶體管每秒開關數百萬次。在開關過程中,被稱為“熱載流子”的高能載流子(電子或空穴)很容易注入并捕獲在柵極氧化物中。這種熱載流子注入會導致柵極氧化物中出現雜質,從而改變器件的 I-V 特性。

這種注射會導致幾個問題。它使NMOS晶體管的工作速度變慢,導致電路失配。它還會導致 PMOS 晶體管出現高電流浪涌,從而導致嚴重的電路故障。

為了對 VLSI 電路中的熱載流子進行仿真或建模,Hsu 等人提出了一種分析方法。al (1991 和 1992) 和 Quader 等人。等人。

負偏壓溫度不穩定性 (NBTI)

NBTI 會導致 p 溝道 MOS 晶體管的閾值電壓增加、遷移率下降、漏極電流和跨導增加。NGTI 發生在高溫下硅/氧化硅界面處存在陷阱的情況下。

由于高溫下的強負偏壓(柵極電壓為 0,源極電壓為 V DD ),這種效應在 PMOS 晶體管中更為突出。NBTI 的主要影響是它導致遷移率降低和閾值電壓增加,從而導致數字電路中的延遲增加。

根據阿拉姆和瑪哈帕特拉的說法;杰普森和斯文森;還有小川和鹽野;NBTI 可以使用反應擴散 (RD) 模型進行建模。保羅等。al 還提出閾值電壓偏移可以建模為

ΔVt=keEoxE0t0.25

隨時間變化的介電擊穿 (TDDB)

TDDB是指存儲在小于材料擊穿強度的恒定電場下的電介質隨著時間的推移而擊穿的物理過程。

在MOS晶體管中,柵極氧化物是電介質;當在柵極氧化物上施加電場時,電流將逐漸增加。當施加電場一定時間時,會導致嚴重的電介質擊穿,從而使柵極短路。

針對 TDDB 的電場依賴性,提出了兩個主要模型:陽極空穴注入 (AHI) 模型和 E ox模型。Moonen 等人對這些模型進行了修訂研究。

電遷移

電遷移經常發生在承載單向電流 (DC) 的電線中。在操作過程中,互連通常會經歷“電子風”,因為高電流密度會導致金屬原子隨著時間的推移而遷移。通常可以通過檢查空隙的形成來觀察(Hu 等人)。

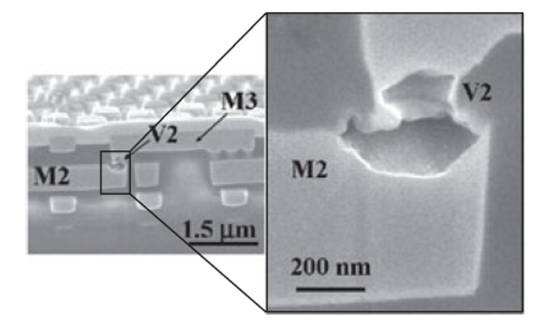

圖 1 顯示了 M2 和 M3 層之間通孔電遷移失敗的顯微照片(Christiansen 等人)。

圖 1. M2-M3 的電遷移失敗。圖片由 Christiansen 等人提供。阿爾

空隙的存在將增加互連的電阻,而小丘的存在將導致不同層互連之間的短路(Jaikaran等人)。

由于電遷移取決于電流密度,J. Black 提出了一個模型,用于計算給定平均故障時間 (MTTF) 和工作溫度 T 下由直流密度 J dc給出的允許電流。

MTTF∝eEakTJndc

其中 E a是活化能

閂鎖

閂鎖是 CMOS 芯片中發生的一種短路現象。CMOS 傾向于在 V DD和 GND之間形成低電阻路徑,從而導致嚴重熔毀并增加 IC 的故障率。理論上,當由襯底、阱和擴散形成的寄生雙極晶體管導通時,就會發生閂鎖。

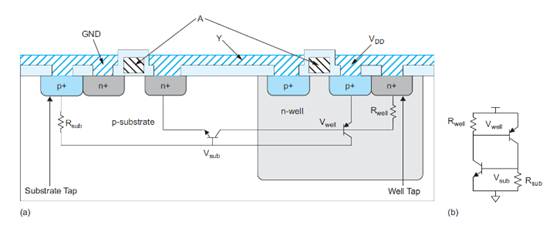

圖 2 顯示了 CMOS 反相器中形成的 BJT 對的等效電路。

圖 2. CMOS 閂鎖模型

除了 NMOS 和 PMOS 晶體管之外,該電路還包含連接到兩個電阻器的 PNP 和 NPN 晶體管,這兩個電阻器連接在電源軌和接地軌之間。電阻器是由附近基板和井抽頭之間的電阻引起的。

通常,BJT 晶體管處于關閉狀態。但當電流流過基板(R sub)時,V sub將上升,這將使 NPN 晶體管導通。結果,NPN 晶體管將電流拉過 Rwell ,從而導通 PNP 晶體管。

PNP 晶體管還將通過 R sub拉動電流,從而提高 V sub。這個循環創建了一個正反饋環路,導致大電流在V DD和GND之間來回流動。如果這個循環持續很長時間,就會產生熱量并熔化電源軌。

幸運的是,可以通過降低襯底和阱之間的電阻來防止閂鎖。實現這一目標的常見方法是將基板和孔抽頭放置在靠近每個晶體管的位置(Neil 和 David)。

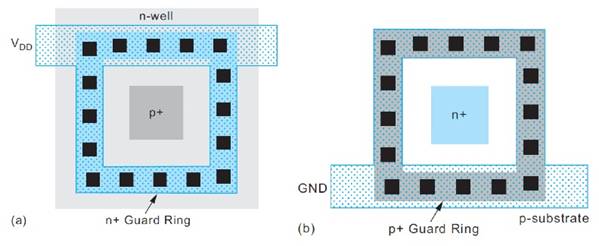

在某些應用中,如圖 3 所示的保護環適合包圍晶體管并在晶體管和電源軌之間提供低電阻路徑。

圖 3.保護環

結論

到目前為止,我們已經討論了 MOS 晶體管的非理想性以及它們如何影響 VLSI 系統的可靠性。已經討論了幾種模型如何測量和模擬它們對設計的影響。

幸運的是,現代 SPICE 模型和 CAD 工具可以全面、準確地預測千兆赫范圍內各種設計的性能,同時考慮到這些非理想的影響。利用這些工具可以推動芯片開發生命周期中的自動化和更快的設計時間。

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理。

推薦閱讀:

千兆多媒體串行鏈路(GMSL)相機用作GigE Vision相機的替代方案