【導讀】專用集成電路的應用使電流監控變得越來越簡單。各種電流監控集成電路隨時買得到,而且多數情況下都工作得很好,還有各種儀表放大器也是如此。

專用集成電路的應用使電流監控變得越來越簡單。各種電流監控集成電路隨時買得到,而且多數情況下都工作得很好,還有各種儀表放大器也是如此。使用分立元件構建電流監控器似乎顯得多余,然而在某些情況下,特別是在有現成的低壓元件時,使用分立元件的電路來進行電流監控可能是最好的方法。

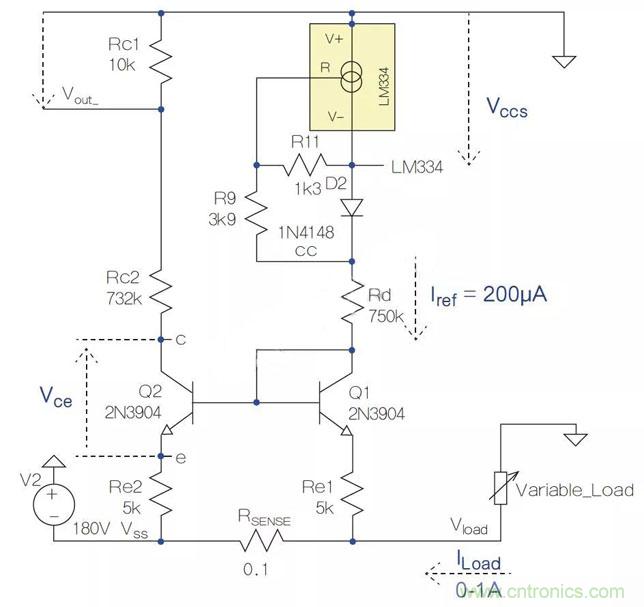

本設計實例中的電路用于監控伺服系統+180/−180V電源的兩個電源軌中的電流。圖1顯示了用于監控負軌的電路相關部分。監控正軌的電路只需用PNP設備替換NPN即可。采用價格便宜的雙晶體管和1%電阻來設置Iref以及Re1和Re2可獲得最佳效果。Rsense應為0.1%并且具有足夠的額定功耗。

圖1:負軌監控電路。

圖1所示電路和所有類似拓撲結構的設計靈感均來自電流鏡拓撲結構,以及Re2上的電流隨Rsense上的電流、Rc1上的電壓隨Rsense上的電壓線性變化的這個概念。

該電路的作用依賴于Re1和Re2。讓Iref相當小而Re2和Re1相當大,當Re2和Re1的值相等時,相對于Rsense上的電壓,發射極的電壓將增加。當負載在無負載和滿負載之間變化時,這將反過來減小輸出設備上Vce的變化。

因此,審慎而明智地選擇Iref、Re1、Re2、Rc2和Rc1可以防止Q2進入飽和狀態并且不會超過晶體管的最大工作電壓。請記住,hoe=I(集電極)/VA(早期電壓)意味著減少Ic的變化也會減少β的變化,從而改善線性度。Rc是Rc1和Rc2之和,因此比率Rc1/Rc確定無負載時Vout−處的偏移。滿載時Rsense上的電壓決定了Re2和Rc1的電流變化,從而決定了Vout−的滿量程輸出。一旦Iref值建立,就可以很容易計算出Rc和Rd上所需的無負載電壓。通過使用發射極電阻,可以顯著降低Vce變化對Q2的β的影響,而且從仿真數據可以看出,β的變化對負載電流和輸出電壓之間相關性的影響相對較小。鑒于這些結果,采用類似于Wilson電流鏡的配置似乎并沒有必要。

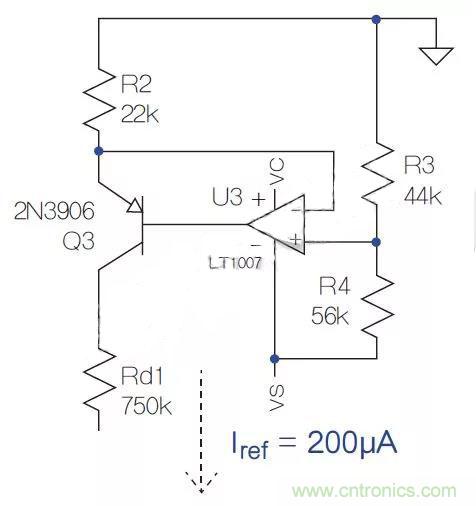

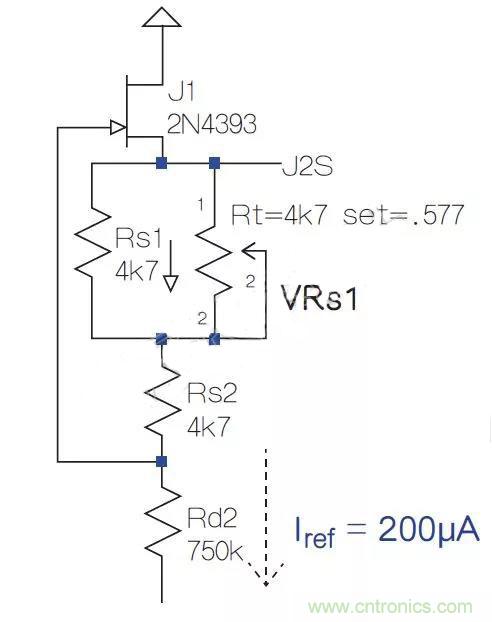

圖2和圖3顯示了用恒流源產生Iref的替代解決方案。如果Vss穩定且沒有紋波,則可以省略恒流源發生器,并且可以通過設定Rd值來提供Iref。

圖2:用恒流源產生Iref的替代解決方案。

圖3:設置FET偏置,使啟動時Iref不會導致Vce或Vds超過最大值。

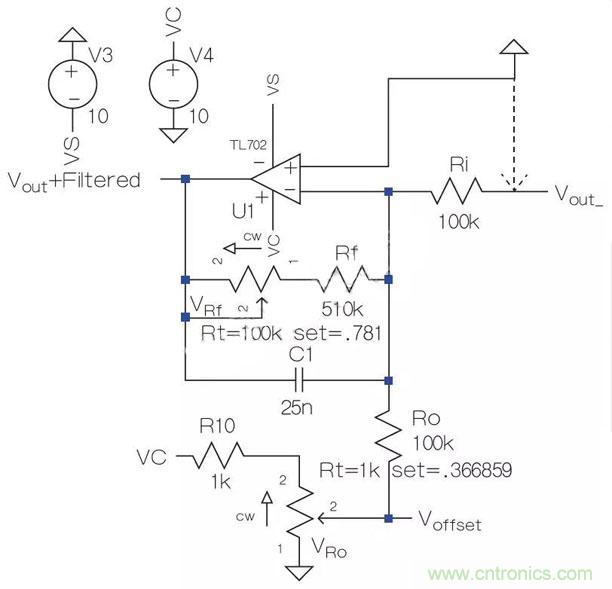

圖4所示的電路反轉了Vout-,消除了偏移,并將輸出調整到所需范圍,同時還可以過濾輸出端出現的電源紋波或負載尖峰。若配以帶有ADC的微控制器,則可以將電路簡化為僅反轉Vout-。

圖4:反轉Vout-消除了偏移,將輸出調整到所需范圍,并可以過濾輸出端的電源紋波或負載尖峰。

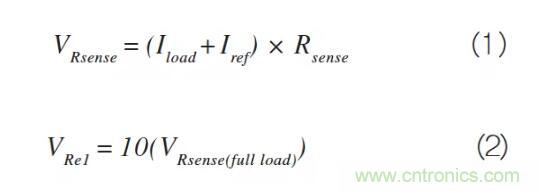

如果滿載時VRe1至少比VRsense大10倍,那么Q2將不會進入飽和狀態,并且:

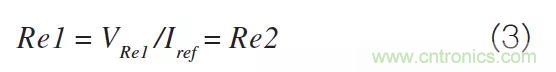

Iref=IRe1,無負載,即Iload=0,那么:

Vccs是恒流源兩端的電壓,IRe1約等于Iref,Vbe可以為0.6到0.65V:

Vce是Q2上無負載時所需的最大電壓。IRe2約等于Iref,那么:

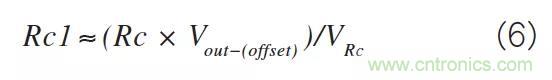

Vout-無負載時所需的失調電壓決定了Rc1的值:

由于I(Rsense)=Iref/10,因此可以估算滿載時的IRe2:

在最大負載電流下,Vout−的滿量程值約為:

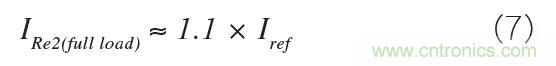

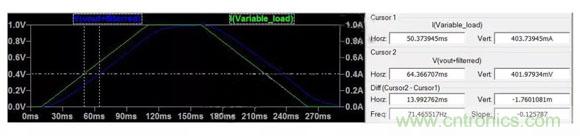

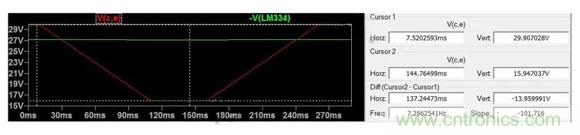

采用LTspice電路仿真軟件產生圖5、圖6和圖7的曲線,以顯示電路工作期間的線性度、濾波效果以及Vce和Vds。負載電流從0增加到1安培,輸出電壓疊加在負載電流上。其結果與實際的電路性能非常接近。

由于負載電流尖峰值持續時間短,濾波防止了跳閘。隔離雖可能沒有必要,但在設計高壓電路時應始終予以考慮。

圖5:將圖4中25nF的電容C1去掉后的Vout。

圖6:圖4中加上25nF電容C1時的Vout。

圖7:有源設備上的電壓。