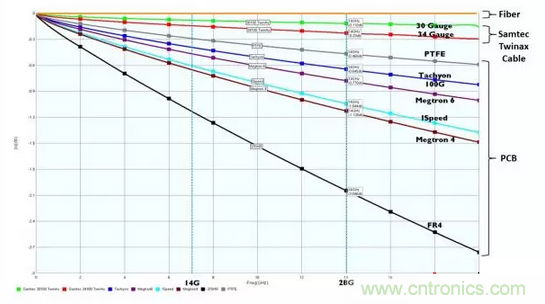

隨著對帶寬需求的不斷增加,對系統內更高數據速率的需求也在不斷增加。曾經1到3Gbps,接著轉向到4到8 Gbps,現在我們接近28 Gbps,并預計進入56 G。這一趨勢最近被推動到DesignCon 2018,許多參展商展示了以112 Gbps運行的互連 PAM 4。

雖然數據通信和電信行業正在努力推動這些前沿的數據速率,但要實現這一性能遠比說起來困難得多。設計挑戰包括PCB上的路由復雜性,以及對更高層數的潛在需求。對于更長的走線長度,可以采用具有較低介電常數和重新定時器的更具奇特性的PCB材料,以減輕降級信號損失。所有這些因素都會增加系統成本。

除了材料和成本之外,設計師還經常面臨成品尺寸減小的挑戰。移動和手持設備的激增推動了這一趨勢,以及電信、高功率計算機、醫療設備、航空航天和國防,甚至工業應用等行業的新要求。

此外,新的高數據速率芯片組(當然設計為產生盡可能少的熱量)仍然產生熱量。這些通常需要更多更大的散熱器,這進一步使設計困境復雜化。

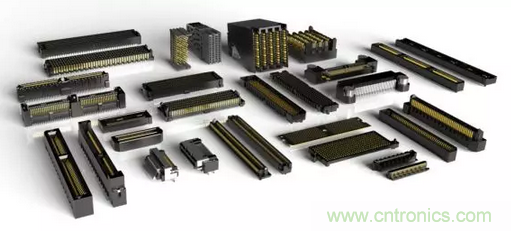

顯然,對更小、更高帶寬PCB的不斷增長的需求推動了互連行業的研發。微間距和高速互連系統的銷售穩步增長。有趣的提醒是大多數高速互連也是微間距。但是,互連的間距越小,實現更高帶寬就越困難。

更小更緊的間距互連系統帶來了一系列新的電氣挑戰,例如串擾和插入損耗。這主要是由于一個差分對與下一個太接近,從而減少了布線空間,減少了接地引腳。

與許多設計挑戰一樣,有幾種方法可以解決這個問題:

PCB布局

設計師可以通過對其電路板布局進行戰略性考慮來緩解這些問題。精心規劃的走線設計和布線、接地位置、過孔等可提高PCB數據速率。PCB設計策略超出了本文的范圍,但存在大量工具、資源和人員來協助這項工作。例如,Samtec擁有Signal Integrity Group和Teraspeed Consulting來協助解決這些問題。

高速微間距互連設計

盡管小型化和更高數據速率的目標存在沖突,但連接器制造商可以在性能和占用空間尺寸方面取得平衡。

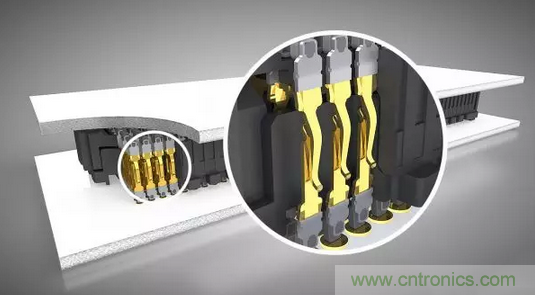

這些連接器設計策略的一個例子是名為EdgeRate®的接觸。該接觸設計用于更高周期的應用,同時適應更高的帶寬。例如,0.8mm間距邊緣速率互連的額定值為56 Gbps PAM4。在帶寬和間距之間實現這種平衡的方法之一是在塑料體中設計和放置銷。具體而言,Edge Rage接觸的薄而窄的切割邊緣并排放置。這使平行表面積最小化,這減少了寬邊耦合和串擾。

提高連接器性能

用于實現高帶寬微間距互連的其他連接器設計策略包括但不限于:

· 在設計的早期階段執行多個模擬循環,以便在開始昂貴的加工過程之前準確地量化產品性能。

· 連接器配對時,最小化接觸區域中的過孔stub。從機械角度來說,過孔stub越長,可靠性越好,但是過孔stub是一種像天線一樣的電氣負荷。

· 簡化接觸幾何形狀,以提高信號路徑性能。

· 縮短引腳長度以最小化信號必須傳播的距離。

· 盡可能包括不對稱的占位和接觸;交替設計減少了引腳行之間和行之間的成對對的串擾。換句話說,占位應該驅動連接器性能。

· 優化連接器分支區域(BOR)。將連接器視為鏈路中的關鍵節點;不僅關注節點,還關注鏈接。

· 在空間允許的情況下,將共同的地平面插入連接器。

塑料成型的產品顯然會影響連接器的性能。在其他問題中,我們仔細考慮以下屬性:

· 適用于RoHS的高溫塑料

· 匹配Dk以獲得所需的阻抗控制

· 溫度和時間的尺寸穩定性

最重要的是,信號路徑(和連接器接觸)越短越直,信號完整性能越好。但平衡作用是連接器必須具有足夠的正向力和拔出力,以及具有一定程度的堅固性。后面的考慮通常會降低信號完整性性能。