- 電容式數字隔離器的基本功能

- 如何簡化隔離系統設計

- 在信號通路中安裝隔離器

- 電路板設計

目前,有關電子設備使用和設計的安全規定層出不窮,使電流隔離器幾乎成為所有數據采集和傳輸系統中的必需。避免控制系統低壓電路在電場中遭受潛在的傳感器和傳動器組件高壓損害的一種方法,就是使用數字隔離器。

本文的目的在于告訴大家如何簡化隔離系統設計,文章除描述電容式數字隔離器的基本功能,詳細介紹如何在信號通路中安裝隔離器外,還就如成功設計電路板提供了一些有價值的參考意見。

電容式數字隔離器的基本功能

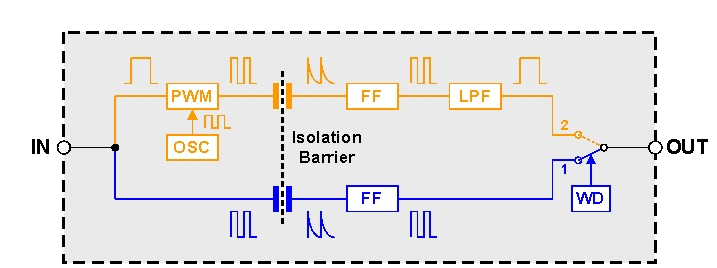

圖1顯示了一個電容式數字隔離器的簡化結構圖,該隔離器由一個高速信號路徑和一個低速信號路徑組成。高速路徑(藍色部分)傳輸100kbps至150Mbps的信號,而低速路徑(橙色部分)則傳輸100kbps以下信號至dc。

低速路徑比高速路徑多出幾個功能元件。因為低頻輸入信號要求隔離勢壘禁止采用大電容,所以輸入信號被用于對內部振蕩器(OSC)的載波頻率進行脈寬調制(PWM)。這就構成了一個非常高的頻率,能夠通過該電容勢壘。由于輸入得到了調制,因此必須在實際數據傳輸至輸出端以前使用低通濾波器(LPF)去除其中的高頻載波。

數字隔離器分為單通道、雙通道、三通道及四通道器件,可以實現單向和雙向運行,它們的共有特性如下:

- 不符合任何特定接口標準;

- 使用3V/5V邏輯開關技術

- 專為電隔離數字、單端(SE)數據線而設計

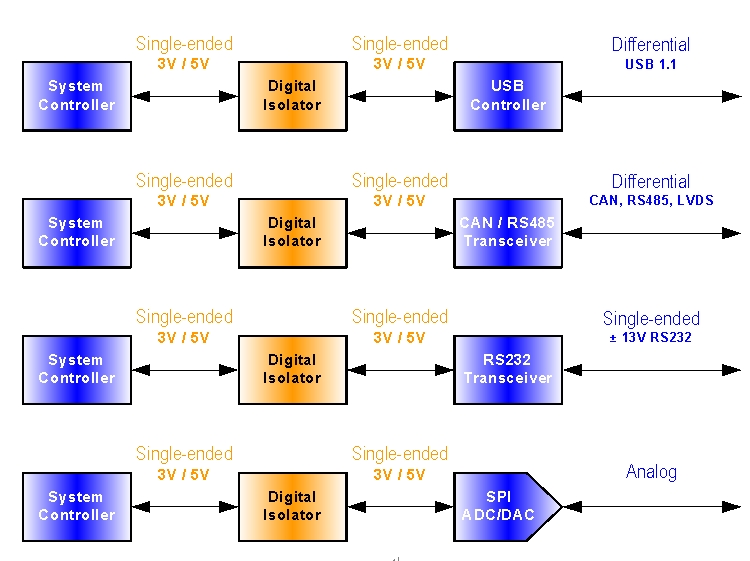

雖然最后一點似乎是設計上的限制,然而圖2卻顯示了如何對多種接口進行隔離,其中包括低壓 SPI、高壓RS232、差分USB和差分CAN/RS485。

圖2 數字隔離器必須安裝在隔離接口的單端部分中

[page]

所有接口都有一個相同點,那就是數字隔離器必須安裝在隔離接口的單端3V/5V部分。

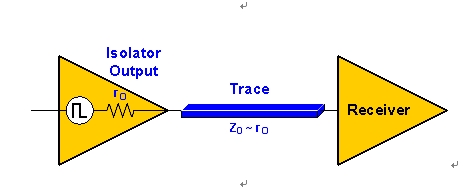

由于數字隔離器都具有1到2ns的升降時間,因此它們在長信號走線情況下往往易出現信號反射,其特性阻抗與隔離器輸出的源阻抗不匹配。因此,我們建議在其相應數據接收裝置和數據源(例如:控制器、驅動器、接收器和收發器等)附近安裝一個隔離器。在設計中如果無法這樣做,那么就必須使用受控的阻抗傳輸線。

PCB 設計指南

就數字電路板而言,要使用標準FR-4環氧玻璃作為PCB材料,這是由于相比那些廉價材料,其不但符合UL94-V0要求,而且還擁有更少的高頻介電損耗、更低的吸濕性、更大的強/硬度以及更高的阻燃特性。

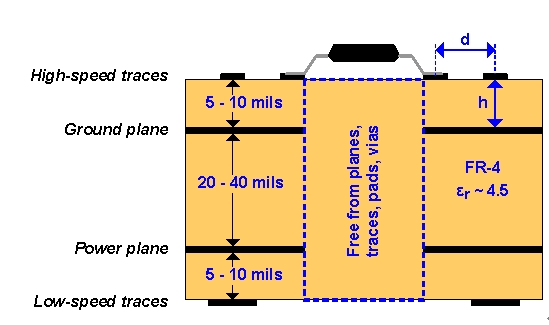

要實現低電磁干擾(EMI)的PCB設計,這里推薦一個最少四層的設計實例(請參見圖3),其從上到下分別為:高速信號層、接地層、電源層以及低頻信號層。

在頂層布置高速走線為隔離器及其相應的驅動器提供了一目了然的連接。高速走線要短,并避免使用過孔,以此保證高速走線電感最低。

緊接著高速信號層放置一個平衡板面地線層,以確保接地層和信號走線之間存在強大的電氣耦合。這樣便建立起傳輸線互聯的受控阻抗,同時也極大地減少了EMI。最終,平衡板面地線層為回流提供了一個非常好的低電感路徑。

將電源層置于接地層下面。這兩個參考層構成了一個大約為100pF/in2的附加高頻旁路電容器。

在底層布線低速控制信號。這些信號鏈路擁有足夠的余量來承受過孔引起的中斷,從而實現了更大的靈活性。

受控阻抗傳輸線是特性阻抗Z0始終受控于其幾何特性的走線。走線長度大于

隔離器的動態輸出阻抗r0,可以通過隔離器數據手冊中列出的近似電壓-電流輸出特性線性部分得到。一般來說,標準輸出阻抗大約為70Ω。因此,對一條標準的

布線指南

建議遵循下列幾條主要的布線原則,以保持信號完整性和低EMI。

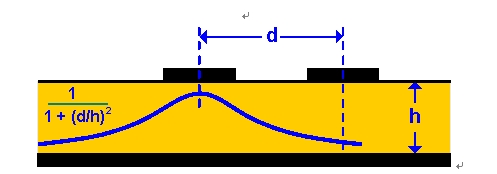

為了將串擾降至10%以下,需保持信號走線是高速信號層到接地層距離的三倍(d=3h)。信號走線下的回流密度遵循1/[1+(d/h)2]函數,因此其在d>3h點上的密度會非常低,從而避免鄰近走線中出現較大的串擾(請參見圖5)。

圖5 利用d = 3h 來最小化串擾

[page]

使用45o走線彎曲(或者斜切式彎曲)而非90o彎曲,可保持有效的走線阻抗并避免信號反射。

為了實現在噪聲環境下的工作,將隔離器的閑置啟動輸入通過一個電阻器(1kΩ到10kΩ)連接到合適的參考層。將高電平有效、高位允許輸入連接到電源層,同時將低電平有效輸入連接至接地層。

當過孔電感增加信號路徑電感時,要避免各層隨快速信號走線改變。

在隔離器與周圍電路之間使用較短的走線長度可避免噪聲引入。數字隔離器通常會帶有隔離式DC/DC轉換器,后者提供了跨越隔離層的電源。由于隔離器的單端傳輸信號對噪聲引入過于敏感,因此鄰近DC/DC轉換器的開關噪聲可以很容易被長信號走線引入。

將大容量電容(比如10μF)置于靠近電源如穩壓器旁,或是在電源進入PCB的地方。

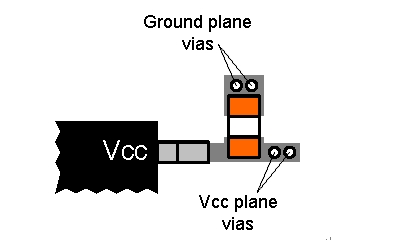

通過將電容的電源端直接連接至器件的電源端,然后經過孔連至Vcc層,在器件上安裝小容量的0.1μF或0.01μF旁路電容。經數個過孔將電容接地端連接至接地層(請參見圖6)。

圖6 將旁路電容直接連接至Vcc 終端

將多個過孔用于連接旁路電容和其他保護器件(例如:瞬態電壓抑制器和齊納二極管),從而最小化接地連接的過孔電感。

總結

盡管關于PCB設計的資料有很多,但本文主要提供一些涉及數字隔離器電路板設計的建議。遵循這些建議將有助于在最短的時間內完成一個符合EMC標準要求的電路板設計。