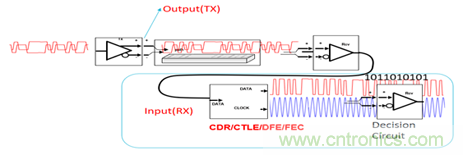

【導讀】在用戶進行系統或者芯片測試的時候,一般主要驗證幾個方面的性能和可靠性,包括系統發送端的信號質量,鏈路的損耗/串擾,接收端的容限。如下圖1,一個鏈路系統的基本架構。通常在發送端會使用FFE來補償鏈路的損耗,接收端會采用DFE/FFE等方法來進行均衡,一些比較高速率的標準如PCIE 4.0/5.0,SAS4等還會采用FEC來進行糾錯,當然接收端還需要CDR來從串行信號里面進行時鐘恢復得到同步時鐘來對信號進行采樣。

圖1:高速串行鏈路的基本架構

對于系統/芯片的接收端測試,會有幾個方面的挑戰,第一是loopback (環回)模式的Training,第二是link(鏈路)training。只有這兩個部分的協商正確完成的前提下,才能保證測試的順利完成。不管是loopback training 還是link training,都要求Bert具備和被測設備自動的協商功能,通過基于協議的握手和雙向溝通去使被測設備進入環回模式和均衡的自適應。

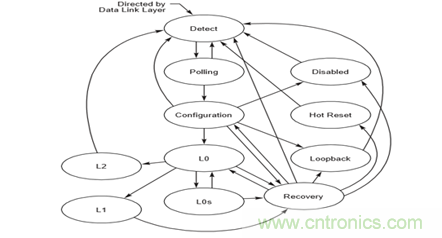

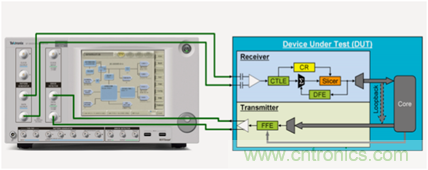

如圖二,支持各種協議的系統/芯片在上電后會通過與對端設備的多次協商進入不同的子狀態機,在接收端容限測試的時候需要使被測芯片的狀態機從Config或者Recovery狀態進入loopback的子狀態,這個實現需要Bert模擬一個真正的對端設備去發送符合該協議的碼型系列去training 被測設備。同時Bert也要能實時的解析被測設備的協議系列以確認其是否被成功training,否則需要重新修改設置來發送training的碼型序列。如圖3,泰克的BSX系列誤碼儀最高可以支持單通道32Gbps的實時數據發送和接收,可以直接產生和接收并同時解析協議的數據包,而不像其他廠商只能在較低速的時候實現數據直接產生和接收,而高速標準則需要通過兩個通道合并成單通道進行發送,并在接收端則將單通道再分解成兩個通道進行接收。這樣會導致高速標準的時候不能實現真正基于協議的協商。

圖2:PCIe/USB3.1等協議標準的各種狀態機。

圖3:BSX系列誤碼儀支持單通道的高速協議數據的發送和接收解析

如圖3,除了loopback training以外,另一個重要的步驟是link training(鏈路協商),需要Bert和DUT進行FFE/DFE的實時協商來補償鏈路的損耗,以達到最低的誤碼率。在USB3.1/PCIe協議中發送端會有多個級別的FFE來靈活對信號發送端進行均衡補償,在接收端也會有CTLE和DFE多級組合來進行補償。(詳細的鏈路協商步驟細節可以參考泰克的相關應用文章-《克服第4代I/O應用中的接收機測試挑戰》)。這個鏈路協商同樣需要Bert能夠在一定程度上去模擬一個真實設備和被測設備進行溝通,解析并響應被測設備的要求去調節信號輸出的FFE參數,并根據誤碼率來請求被測設備調節其輸出的FFE參數和接收端的CTLE/DFE參數,以達到最佳的誤碼率。同樣這個時候也需要BERT具備單通道直接輸出和接收并解析基于協議的碼型序列達到與被測設備的實時協商。

除了進行一致性測試以外,對于芯片的驗證過程中還經常會進行問題定位,當出現誤碼的時候,大部分工程師會去搬一臺示波器來使用示波器觀察信號波形來進行抖動和眼圖分析來進行調試,這時候得把信號重新連接到示波器來進行信號的捕獲,而且并不容易把誤碼和示波器捕獲的波形直接關聯起來找到誤碼的原因。往往你旁邊并沒有一臺高帶寬示波器供你隨意使用。由于泰克的BSX系列誤碼儀能夠精確的統計誤碼的個數和誤碼出現的時間,所以能夠實現精準的誤碼定位。這個強大的誤碼定位功能和抖動眼圖分析功能可以供你進行系統和芯片級別的調試,下面會舉一些真實用戶使用Bert進行調試分析的實例來說明。

案例一:使用誤碼儀Error Free interval功能來驗證芯片的自適應時間。

客戶在做芯片IP的選型驗證,該芯片支持的速率為20.62bps,不同IP廠商會給出不同的芯片自適應時間,一般為幾百微妙到幾百毫秒不等,如前面所述,有一些芯片的關鍵參數會影響到這個自適應時間,如芯片的FFE/DFE的均衡自適應時間,CDR的鎖定時間,誤碼判決電路的采樣點的自動調節等。客戶的需求是測試從芯片開始初始化那一刻直至誤碼率低至10^-12左右的時間。

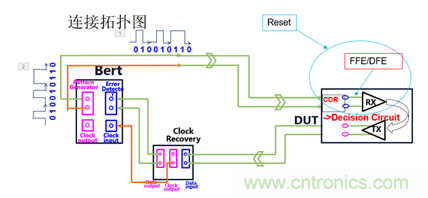

圖4:連接拓撲圖

先按照上面圖4的連接圖連接好,將被測芯片設置為環回模式,設置Bertscope的PG輸出為被測速率,碼型設置為PRBS31,確認CDR模塊可以正確鎖定,Error Detector能夠正確的Sync碼型,并且測試沒有誤碼。將Bert 的Error Detector端設置為Auto-resync。

然后選擇Bert scope的View里面的誤碼分析功能(Error analysis),選擇Error free interval。點擊Error free interval界面,設置,Hist的end 為500000(bit),這個參數需要根據芯片的特性靈活調節,如果芯片的自適應時間較長,則可以適當增加,以保證整個自適應過程的誤碼變化情況都能夠在所選的時間范圍之內。這個界面的橫軸是bit,可以根據信號的速率轉化為絕對的時間,縱軸是誤碼個數。我們可以根據誤碼的變化從而計算出自適應的收斂時間。設置好以后點擊auto center。然后點擊Run。

設置好誤碼儀后,用命令將芯片的RX部分進行一次hot reset,這時候芯片會進行一次時鐘恢復的同步,重新調節DFE,FFE,在Bertscope的Error Free interval里面就可以看到出現大量誤碼然后再慢慢減少到沒有誤碼的過程。在300000bit左右就不再出現誤碼,表示這個時候自適應過程就已經完成。為了保證測試結果的重復性和一致性,建議將這個hot reset的過程做十次,Error free interval會自動將這十次的結果進行疊加。從測試的結果看,芯片的自適應時間約為250000X(1/20.62G)約為12.5us左右。

案例二:使用誤碼的Strip chart的記錄功能來進行長時間的誤碼分析。

由于客戶的系統要進行長時間的(-20到+80度下)的高低溫老化測試,客戶要看誤碼的性能和溫度變化的相關性,一般的誤碼儀只能統計溫度變化過程中誤碼的總的個數和誤碼率,而無法得知在整個十幾個小時里面任一時刻誤碼率的變化。而BSX系列誤碼儀則可以使用Strip chart的記錄功能將整個過程中記錄下來,后面可以根據需要查詢任意時刻的誤碼率變化情況。如下圖,在第10/20/30秒的時間點出現了一些突發的誤碼,這個如果僅僅是通過簡單的誤碼統計是無法看到時間相關的細節的,而且其累積記錄時間可以長達幾十小時甚至幾天。

圖5:使用Strip chart功能記錄整個長時間老化過程誤碼變化

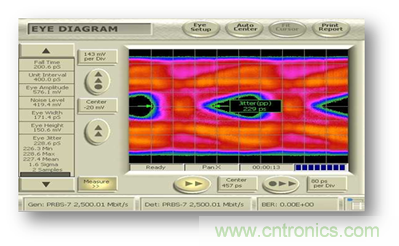

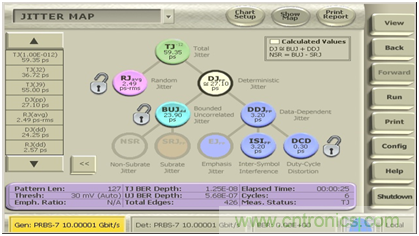

案例四:使用誤碼儀的眼圖和抖動分析功能進行信號特性的分析。

1.客戶在測試誤碼的同時想快捷的觀察TX端輸出信號的質量,確保芯片輸出的信號是否滿足一定的要求。2.客戶想真正的測試10^12次方下的總體抖動的值,因為一般示波器的Tj都是通過測量RJ和DJ然后再通過一定的外推算法去得到10^12 次方下的抖動的,由于示波器存儲深度和計算時間的限制,無法得到真正的Tj@10^12。但誤碼儀是可以通過連續bit的測量從而得到真正的10^12的抖動的,并且其內置的帶有兩個1bit的ADC在實時全速的對每個bit進行掃描和比較,所以能夠快速的得到信號的眼圖(如圖7)。并根據每個bit的與采樣點的偏差計算該bit的TIE的抖動偏移量,從而通過算法計算信號的Rj/Dj并進行抖動的進一步細分。同時由于BSX系列的誤碼檢測輸入端的帶寬高達22GHz以上,所以對高速信號的眼圖和抖動分析的精度非常高。

圖6:Bertscope的誤碼檢測端自帶的兩個1bit ADC的比較器

圖7:眼圖分析功能

圖8:抖動分析功能

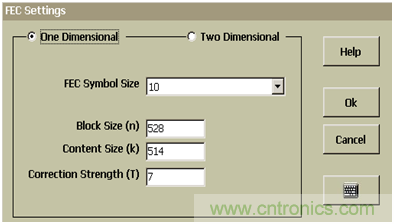

案例五:使用誤碼儀的FEC emulation 功能快速模擬芯片的FEC算法。

由于現在芯片和標準的速率越來越高,為了加強容錯能力,如SAS4/PCIe 4.0/5.0/25G以太網的標準都廣泛使用了FEC來進行糾錯,即便是犧牲了一些額外的開銷,但能夠很大的降低誤碼率,也是值得的。

客戶的芯片的接收端可以支持FEC的糾錯功能,但要測試在不同的channel條件和不同的發送端均衡的設定下,芯片經過FEC后的誤碼率能降低到多少,如果將信號直接環回到芯片的輸入端的話,需要不停的修改芯片的FEC的參數來進行測試,但由于其芯片每修改一次FEC的參數如FEC的symbol size, block size,content size等等都需要重新對芯片進行代碼編譯和下載,每次下載需要幾分鐘的時間,由于不同的條件都要測試,則組合數量很多,導致測試效率非常低。

但是BSX系列誤碼儀的FEC功能能夠靈活實時的調節上述各種FEC的參數,并且實時的更新經過FEC后的誤碼率變化情況,而完全不需要重新下載芯片的代碼(如圖11和圖12)。大大的提高了測試和調試的效率,而且客戶也做過認真的對比,誤碼儀對FEC后計算得到的誤碼率和其真實芯片經過FEC的誤碼率是非常匹配的。這個功能使客戶之前幾天的時間進行調試過程縮短到一天之內完成,作為泰克工程師的我之前也沒有怎么用過這個功能,覺得它是個雞肋,當現場看到客戶的調試過程后也是感嘆不已。

圖9:用戶的測試拓撲結構

圖10:RS-FEC的設定,可以任意修改,即使生效。

圖11:FEC的仿真功能,實時計算出FEC之前和之后的誤碼率的變化。

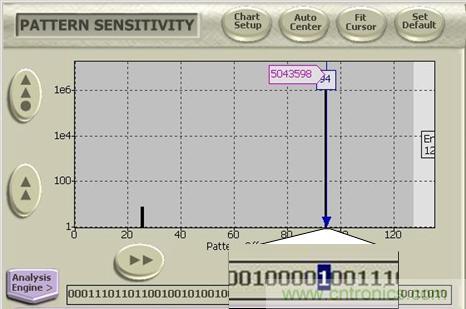

案例六:使用BSX的pattern sensitivity的功能定位誤碼出現的特定比特位.

在客戶進行誤碼測試的時候,由于鏈路的損耗和芯片的輸出特性,導致出現了誤碼,但客戶卻想知道究竟是哪一個bit位出現了誤碼,以定位誤碼出現的根源。設置Bert的輸出/輸入端設置為PRBS7的碼型,在誤碼分析功能里面選擇Patten Sensitivity,則可以直接觀察PRBS7的127個比特的每一位所出現誤碼的個數,看最多誤碼所對應的比特位的前后特性,如下圖十三,移動光標到任意一個比特上面,可以看到連續多個0而中間有一個1跳變的bit即127比特的第94比特出現誤碼的個數最多,達到5043598個誤碼。從而判斷由于鏈路ISI的影響導致突然的跳變位出現較高的誤碼率。

圖12:基于碼型系列的誤碼定位

從上述的用戶實際案例可以看出,Bertscope 的眼圖抖動和誤碼定位分析可以給客戶帶來很多調試的手段,把時域和誤碼極好的相關聯起來,幫用戶極大的提高了測試和調試的效率。

推薦閱讀:

推薦閱讀: